Documentos de Revisão de Projeto de Exemplo

Standard ERC looks at nets. Tomachie looks at paths — verifying differential pair integrity and impedance continuity across the entire signal chain, even through passive components and connectors. It finds what's hidden: mischaracterized pins, broken impedance paths, and invisible property errors that break your layout wizards. These pre-generated reports show the full analysis output, each containing 10,000+ words of DFT analysis, EMC checks, PCOLA-SOQ scoring, connector pinouts, and testpoint coverage documentation:

- Revisão de Projeto FPGA1394V3 — Interface IEEE 1394 FireWire com FPGA Xilinx XC7Z020, análise de boundary scan BSDL, validação de cadeia JTAG

- Revisão de Projeto MB1191 — Placa de desenvolvimento STM32 Nucleo-144 com processador ARM Cortex-M

- Revisão de Projeto TIDA-050036 — Projeto de referência de placa base industrial da Texas Instruments

Amostras para Experimentar

- FPGA1394V3.zip — Interface IEEE 1394 FireWire com FPGA Xilinx, hierarquia multi-folha

- MB1191.zip — Placa de desenvolvimento STM32 Nucleo-144 (ST Microelectronics)

- TIDA-050036.zip — Projeto de referência de placa base industrial da Texas Instruments

Baixe qualquer amostra, envie na página Enviar e receba um relatório completo de análise.

Exemplo de Saída do Relatório

Tomachie gera um relatório HTML interativo com seções navegáveis. Veja o que você receberá:

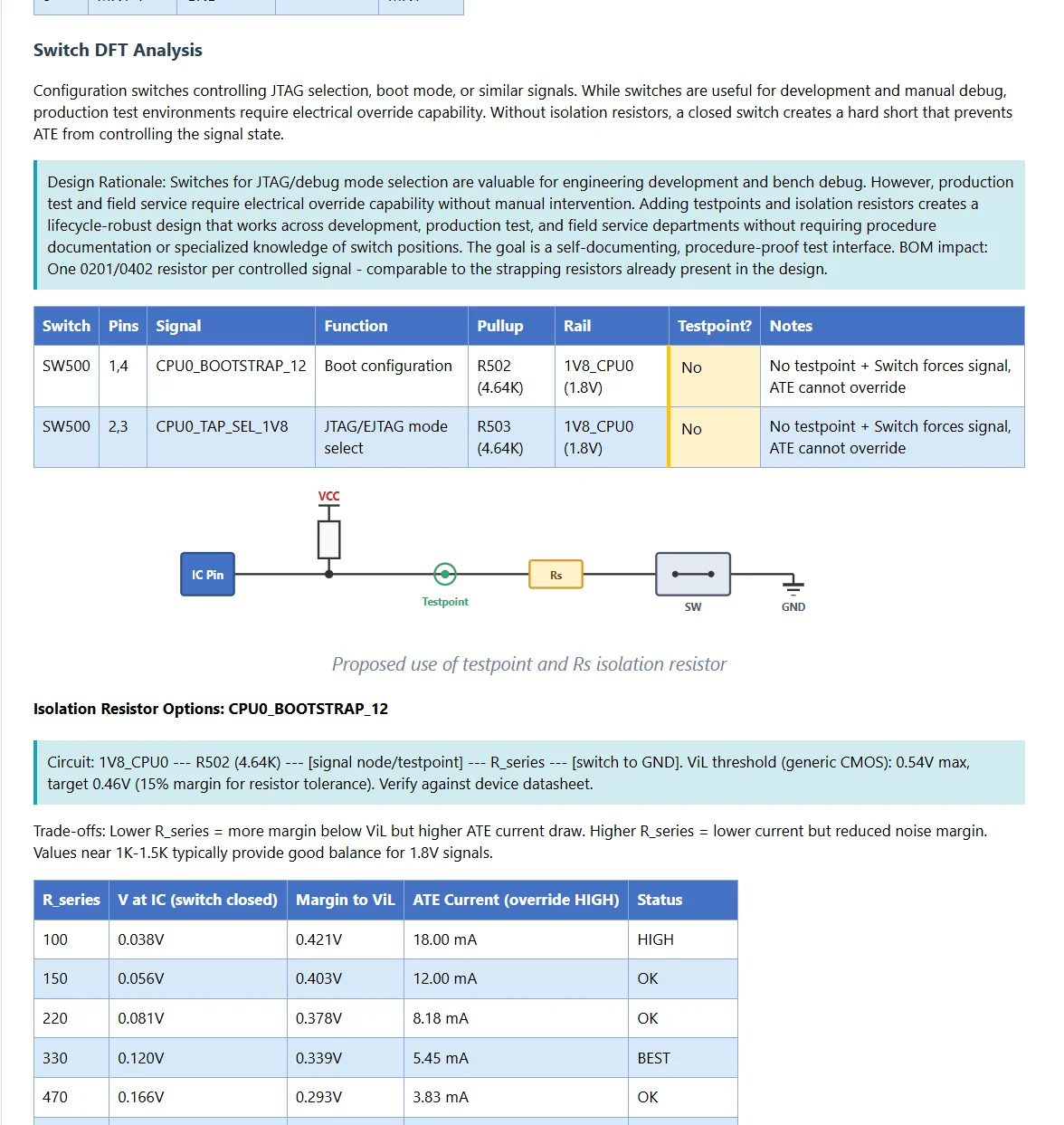

Análise DFT de chaves — identifica chaves de configuração sem capacidade de sobreposição de teste, calcula valores de resistor de isolamento para compatibilidade ATE.

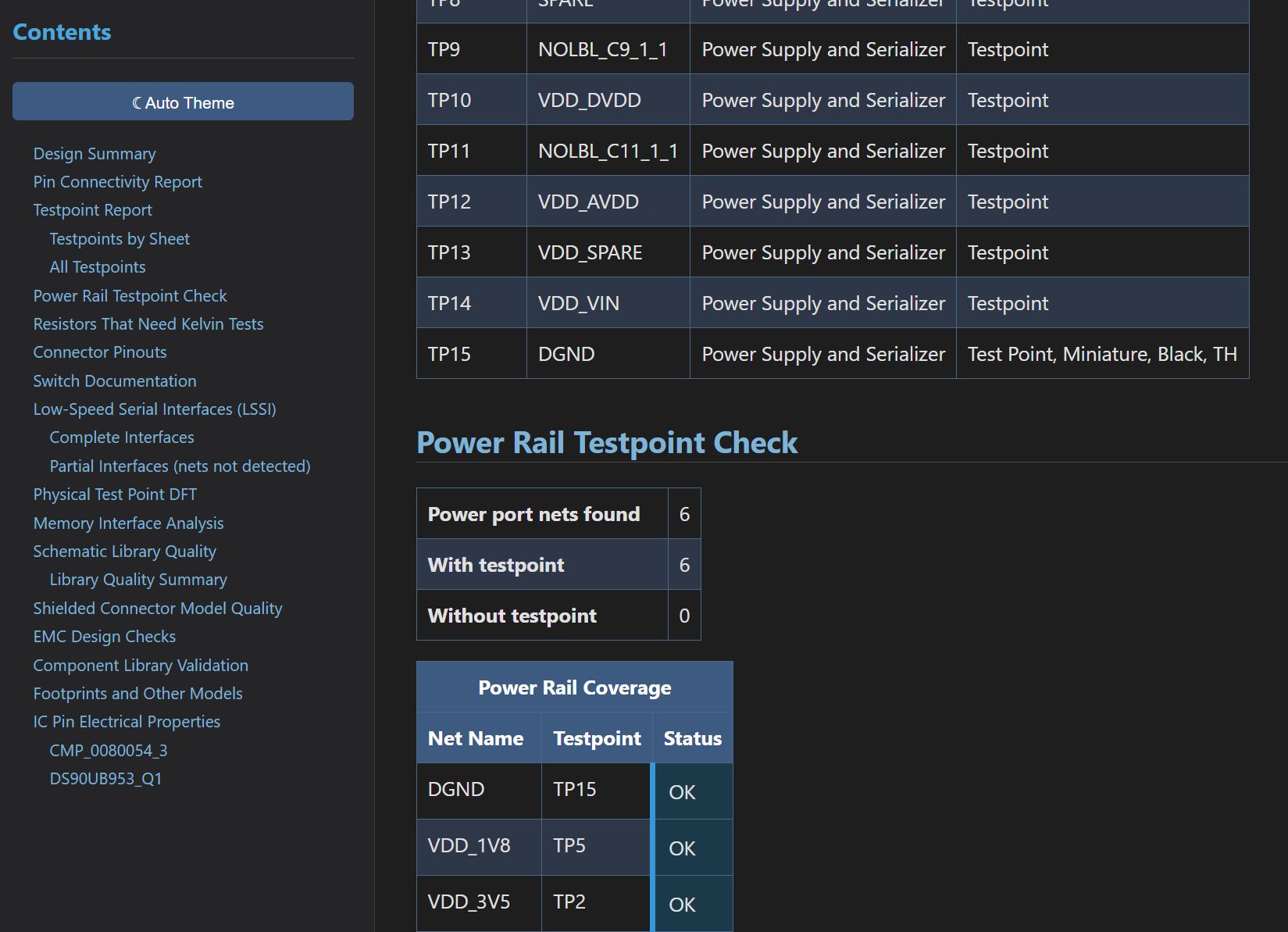

Inventário de pontos de teste com análise de cobertura de trilhas de alimentação — cada rede de alimentação verificada quanto ao acesso de teste.

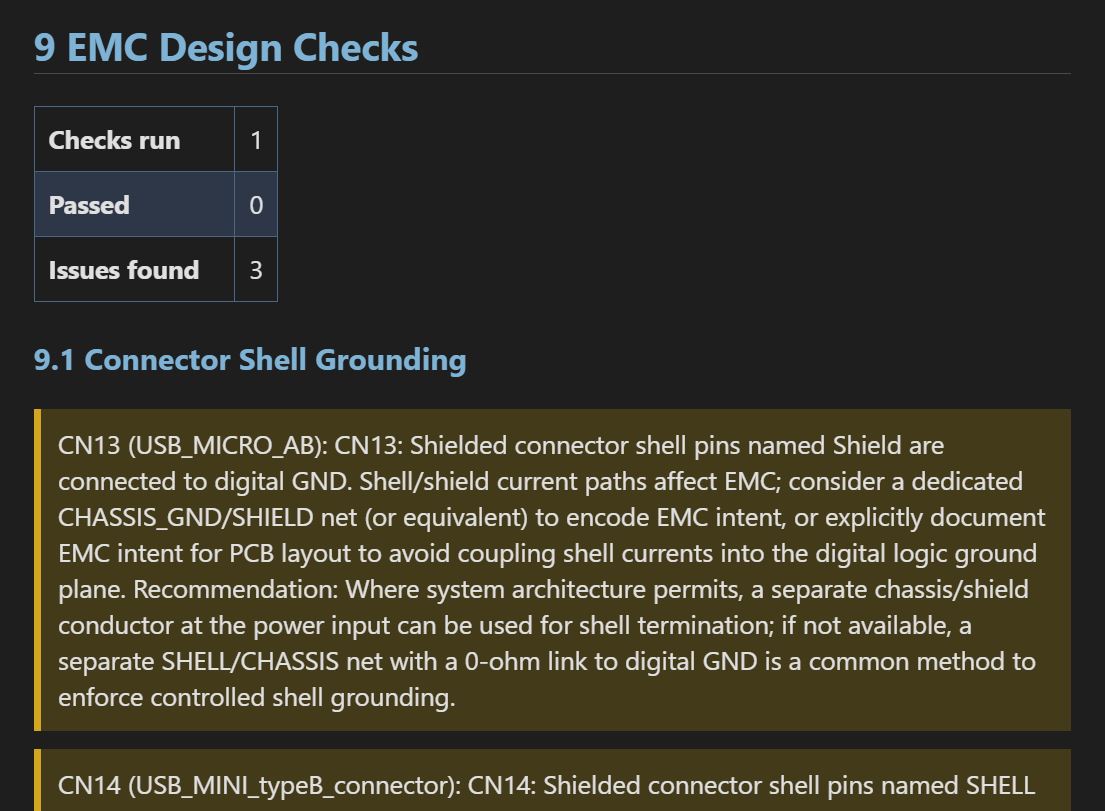

Verificações de projeto EMC, validação de biblioteca de componentes e auditoria de footprint/modelo — tudo em um relatório.

O painel de navegação à esquerda permite ir diretamente a qualquer seção. Os relatórios incluem Resumo do Projeto, Conectividade de Pinos, Interfaces de Memória, Interfaces Seriais, Pinagem de Conectores, Análise DFT, Notas de Qualidade de Biblioteca e mais.

Foco Atual: Projetos digitais e de sinal misto — processadores, FPGAs, interfaces de memória, barramentos seriais e análise de testabilidade. Verificações específicas de analógico (estabilidade de malha de fonte de alimentação, análise de filtros) estão no roadmap.

O Que Enviar

Compacte seus arquivos de esquemático em ZIP e envie. Aqui está o que precisamos:

Arquivos de esquemático (obrigatório)

Arquivos Altium .SchDoc ou KiCad .kicad_sch — inclua todas as folhas referenciadas pela hierarquia.

Arquivos de projeto (recomendado)

Altium: .PrjPcb, .PrjPcbStructure, .PrjPcbVariants. KiCad: .kicad_pro. Estes nos informam a hierarquia e a folha principal. Sem eles, você precisará especificar o nome da folha principal, ou assumiremos um projeto plano.

Arquivos *.bsdl (opcional)

Arquivos Boundary Scan Description Language. Estes arquivos usam IEEE 1149.1-2013 para descrever a capacidade de teste dos CIs digitais. Se fornecidos, o Tomachie analisará a correção, conformidade e Design-for-Test do seu projeto.

Dica: Ao solicitar esquemáticos de um projetista ou contratado, peça os arquivos de projeto (.PrjPcb ou .kicad_pro) junto com os arquivos de esquemático. Muitos projetistas esquecem de incluí-los.