نماذج وثائق مراجعة التصميم

Standard ERC looks at nets. Tomachie looks at paths — verifying differential pair integrity and impedance continuity across the entire signal chain, even through passive components and connectors. It finds what's hidden: mischaracterized pins, broken impedance paths, and invisible property errors that break your layout wizards. These pre-generated reports show the full analysis output, each containing 10,000+ words of DFT analysis, EMC checks, PCOLA-SOQ scoring, connector pinouts, and testpoint coverage documentation:

- مراجعة تصميم FPGA1394V3 — واجهة IEEE 1394 FireWire مع Xilinx XC7Z020 FPGA وتحليل المسح الحدودي BSDL والتحقق من سلسلة JTAG

- مراجعة تصميم MB1191 — لوحة تطوير STM32 Nucleo-144 مع معالج ARM Cortex-M

- مراجعة تصميم TIDA-050036 — تصميم مرجعي للوحة قاعدة صناعية من Texas Instruments

نماذج يمكنك تجربتها

- FPGA1394V3.zip — واجهة IEEE 1394 FireWire مع Xilinx FPGA وتسلسل هرمي متعدد الأوراق

- MB1191.zip — لوحة تطوير STM32 Nucleo-144 (ST Microelectronics)

- TIDA-050036.zip — تصميم مرجعي للوحة قاعدة صناعية من Texas Instruments

حمّل أي نموذج، ارفعه في صفحة الإرسال، واحصل على تقرير تحليل كامل.

مثال على مخرجات التقرير

يُنشئ Tomachie تقريراً تفاعلياً بصيغة HTML مع أقسام قابلة للتنقل. إليك ما ستحصل عليه:

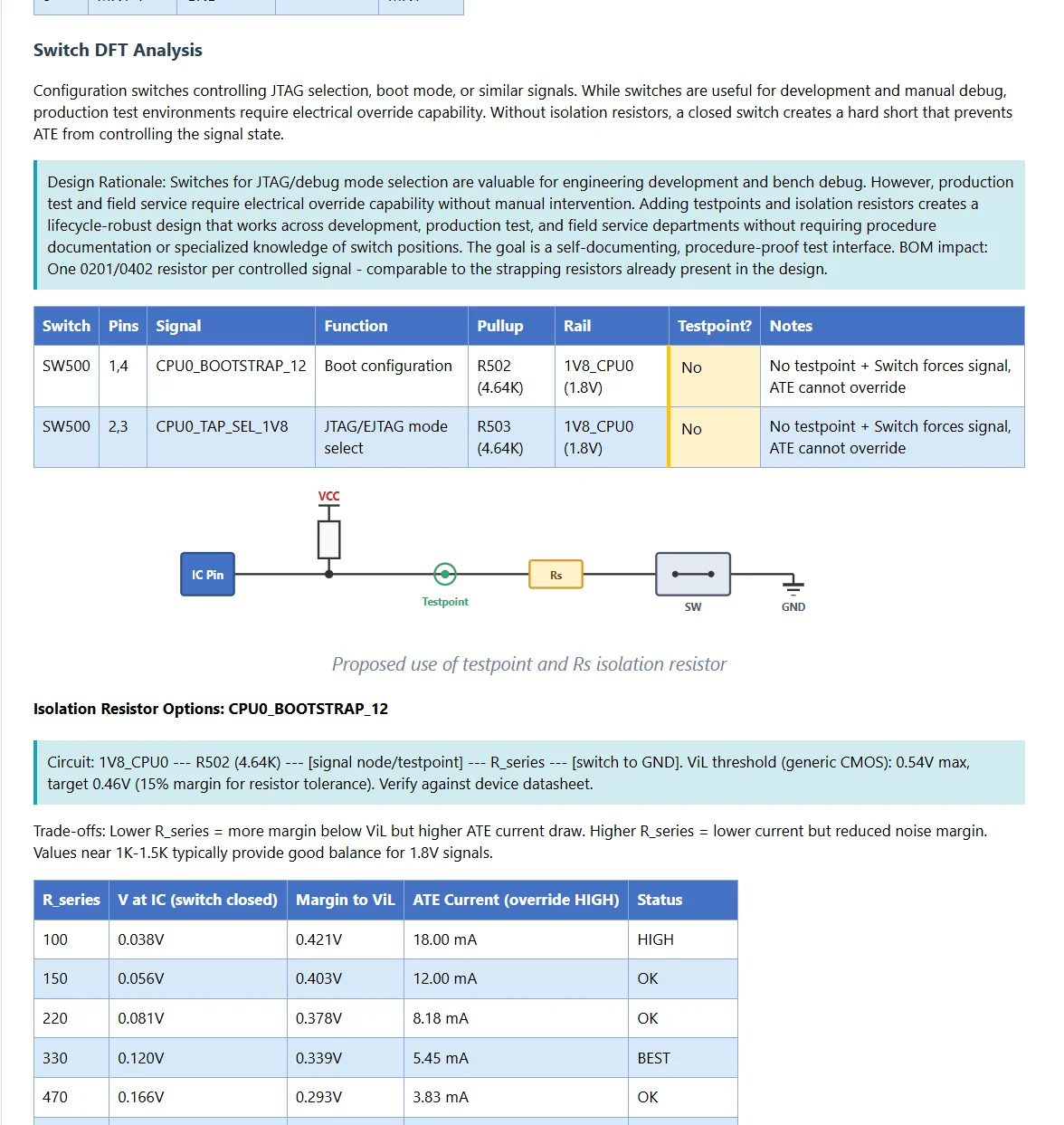

تحليل DFT للمفاتيح — يحدد مفاتيح التكوين التي تفتقر لإمكانية تجاوز الاختبار، ويحسب قيم مقاومة العزل لتوافق ATE.

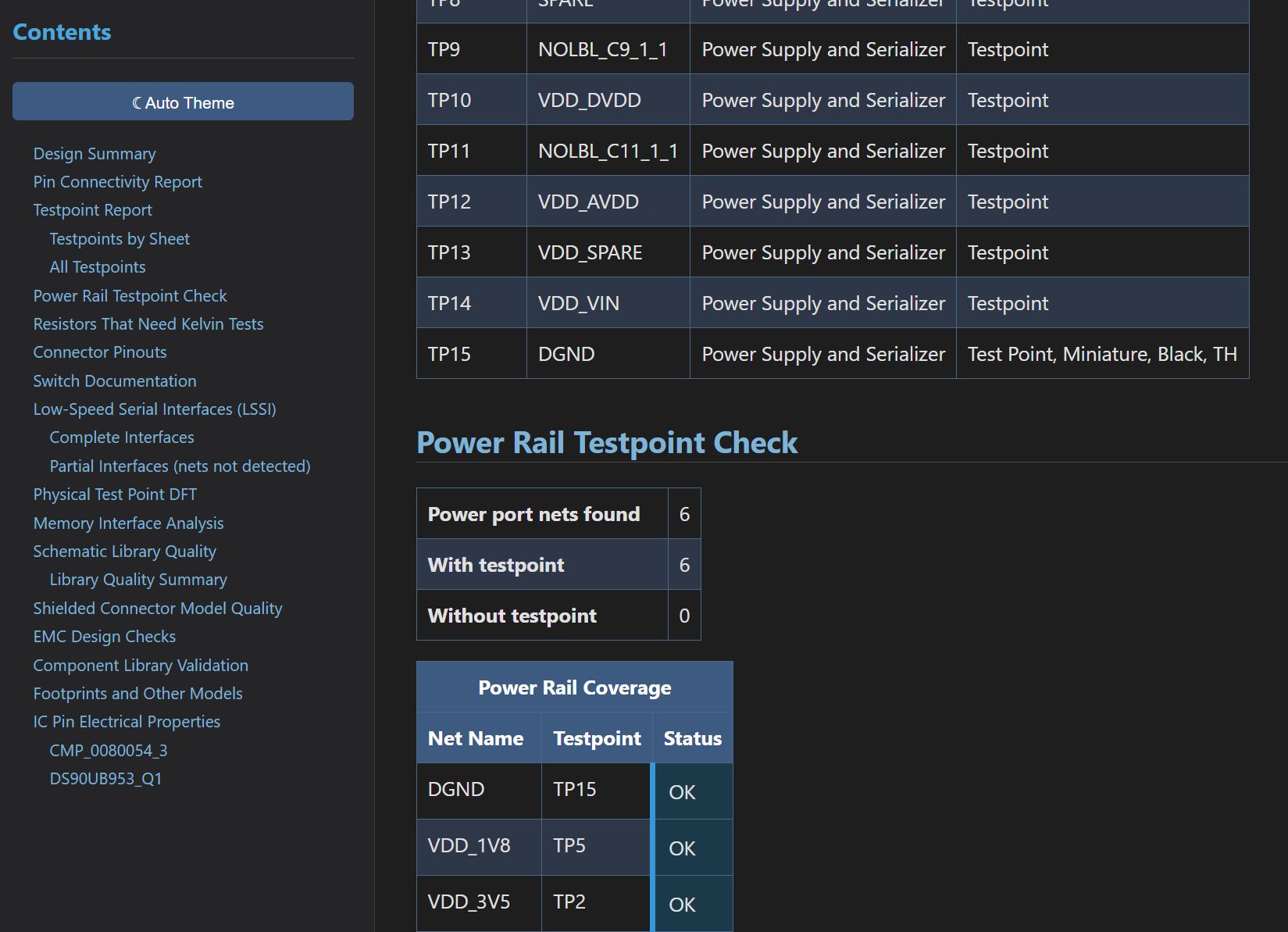

جرد نقاط الاختبار مع تحليل تغطية خطوط الطاقة — كل شبكة طاقة تُفحص للوصول الاختباري.

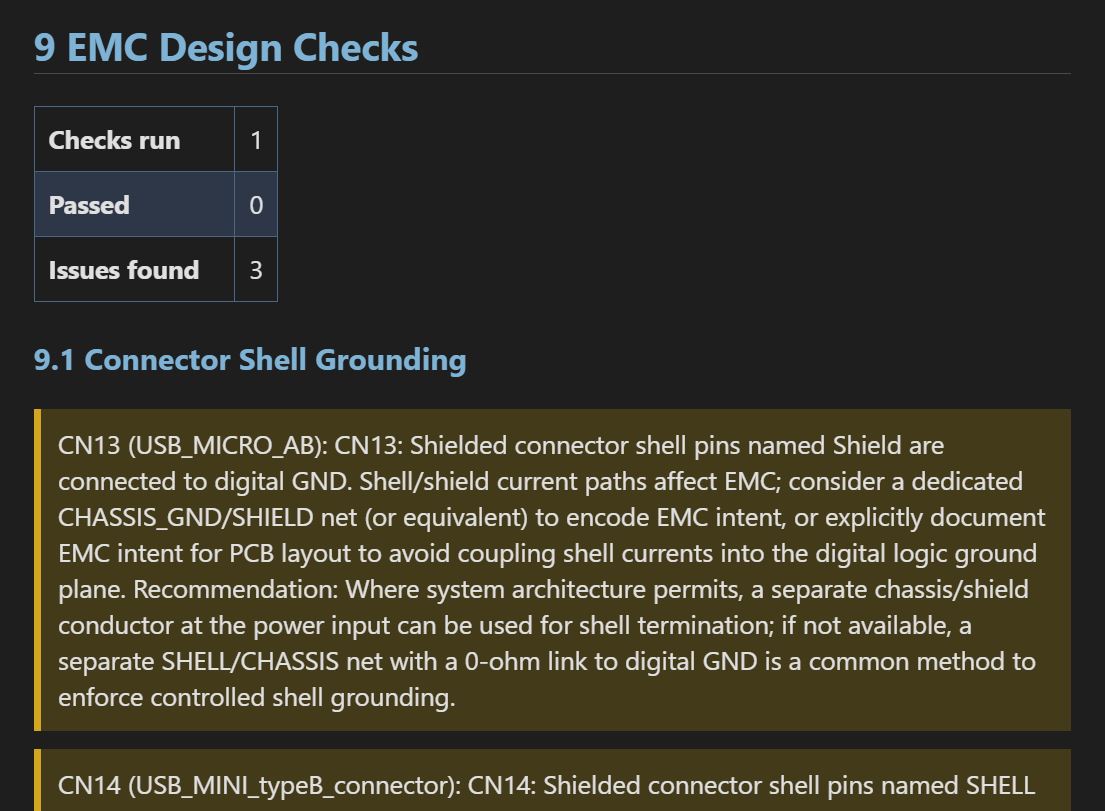

فحوصات تصميم EMC والتحقق من مكتبة المكونات ومراجعة البصمة/النموذج — كل ذلك في تقرير واحد.

تتيح لوحة التنقل اليسرى الانتقال مباشرة إلى أي قسم. تشمل التقارير ملخص التصميم وتوصيل الأطراف وواجهات الذاكرة والواجهات التسلسلية وأطراف الموصلات وتحليل DFT ودرجات جودة المكتبة والمزيد.

التركيز الحالي: التصاميم الرقمية والمختلطة — المعالجات وFPGA وواجهات الذاكرة والنواقل التسلسلية وتحليل القابلية للاختبار. فحوصات خاصة بالتناظرية (استقرار حلقة مصدر الطاقة وتحليل المرشحات) على خارطة الطريق.

ما يجب رفعه

اضغط ملفات المخطط بصيغة ZIP وارفعها. إليك ما نحتاجه:

ملفات المخطط (مطلوب)

ملفات Altium .SchDoc أو KiCad .kicad_sch — ضمّن جميع الأوراق المُشار إليها في التسلسل الهرمي.

ملفات المشروع (موصى به)

Altium: .PrjPcb، .PrjPcbStructure، .PrjPcbVariants. KiCad: .kicad_pro. تُخبرنا هذه بالتسلسل الهرمي والورقة العليا. بدونها، ستحتاج لتحديد اسم الورقة العليا، أو سنفترض تصميماً مسطحاً.

ملفات *.bsdl (اختياري)

ملفات لغة وصف المسح الحدودي. تستخدم هذه الملفات IEEE 1149.1-2013 لوصف قدرة اختبار الدوائر المتكاملة الرقمية. إذا تم توفيرها، سيحلل Tomachie صحة وامتثال وقابلية اختبار التصميم.

نصيحة: عند طلب المخططات من مصمم أو مقاول، اطلب ملفات المشروع (.PrjPcb أو .kicad_pro) مع ملفات المخطط. كثير من المصممين ينسون تضمينها.