Documentos de Ejemplo de Revisión de Diseño

Standard ERC looks at nets. Tomachie looks at paths — verifying differential pair integrity and impedance continuity across the entire signal chain, even through passive components and connectors. It finds what's hidden: mischaracterized pins, broken impedance paths, and invisible property errors that break your layout wizards. These pre-generated reports show the full analysis output, each containing 10,000+ words of DFT analysis, EMC checks, PCOLA-SOQ scoring, connector pinouts, and testpoint coverage documentation:

- Revisión de Diseño FPGA1394V3 — Interfaz IEEE 1394 FireWire con FPGA Xilinx XC7Z020, análisis de boundary scan BSDL, validación de cadena JTAG

- Revisión de Diseño MB1191 — Placa de desarrollo STM32 Nucleo-144 con procesador ARM Cortex-M

- Revisión de Diseño TIDA-050036 — Diseño de referencia de placa base industrial de Texas Instruments

Muestras que Puede Probar

- FPGA1394V3.zip — Interfaz IEEE 1394 FireWire con FPGA Xilinx, jerarquía de múltiples hojas

- MB1191.zip — Placa de desarrollo STM32 Nucleo-144 (ST Microelectronics)

- TIDA-050036.zip — Diseño de referencia de placa base industrial de Texas Instruments

Descargue cualquier muestra, cárguela en la página de Envío y reciba un informe de análisis completo.

Salida de Informe de Ejemplo

Tomachie genera un informe HTML interactivo con secciones navegables. Esto es lo que recibirá:

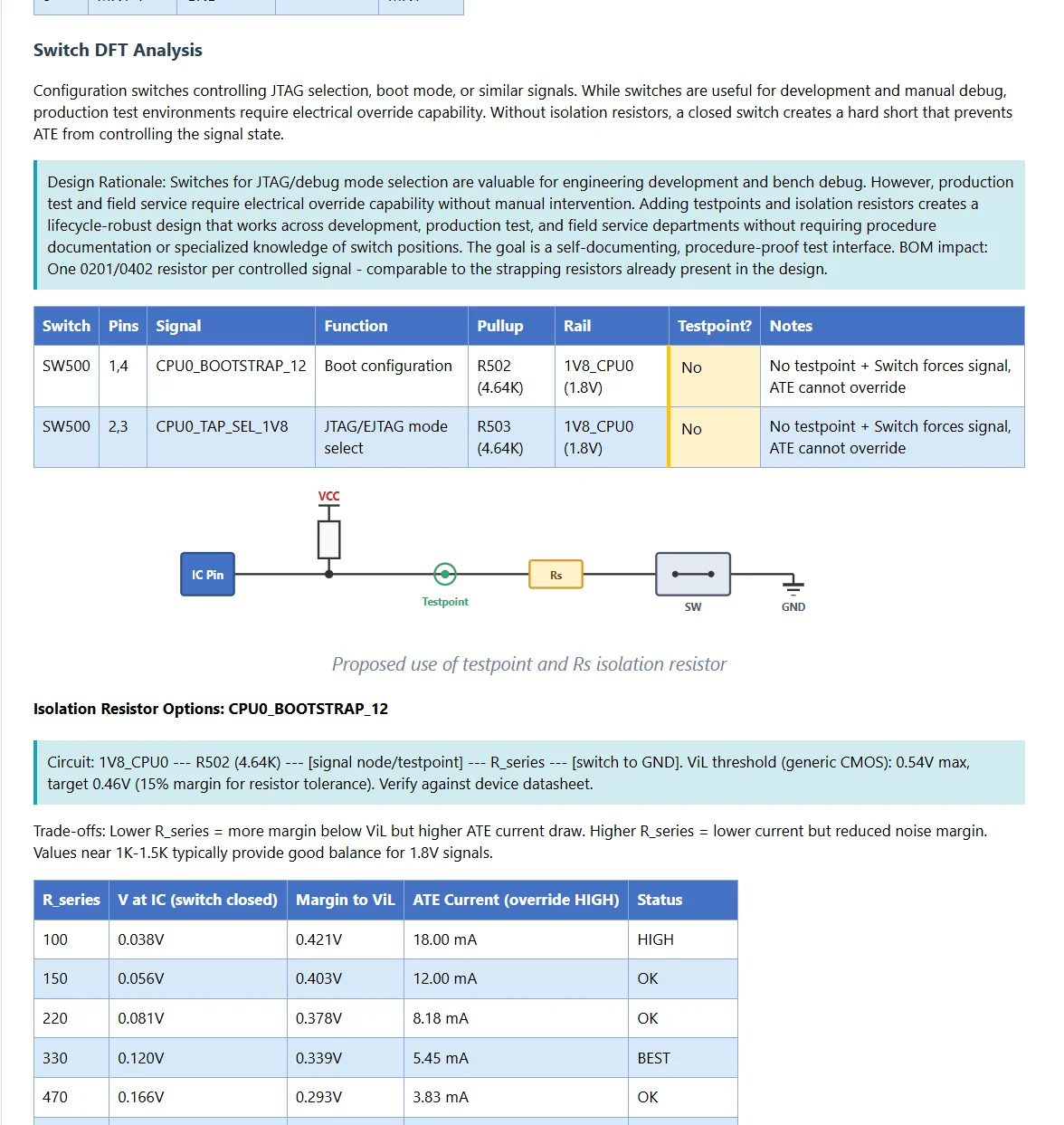

Análisis DFT de switches — identifica switches de configuración sin capacidad de anulación de prueba, calcula valores de resistencias de aislamiento para compatibilidad con ATE.

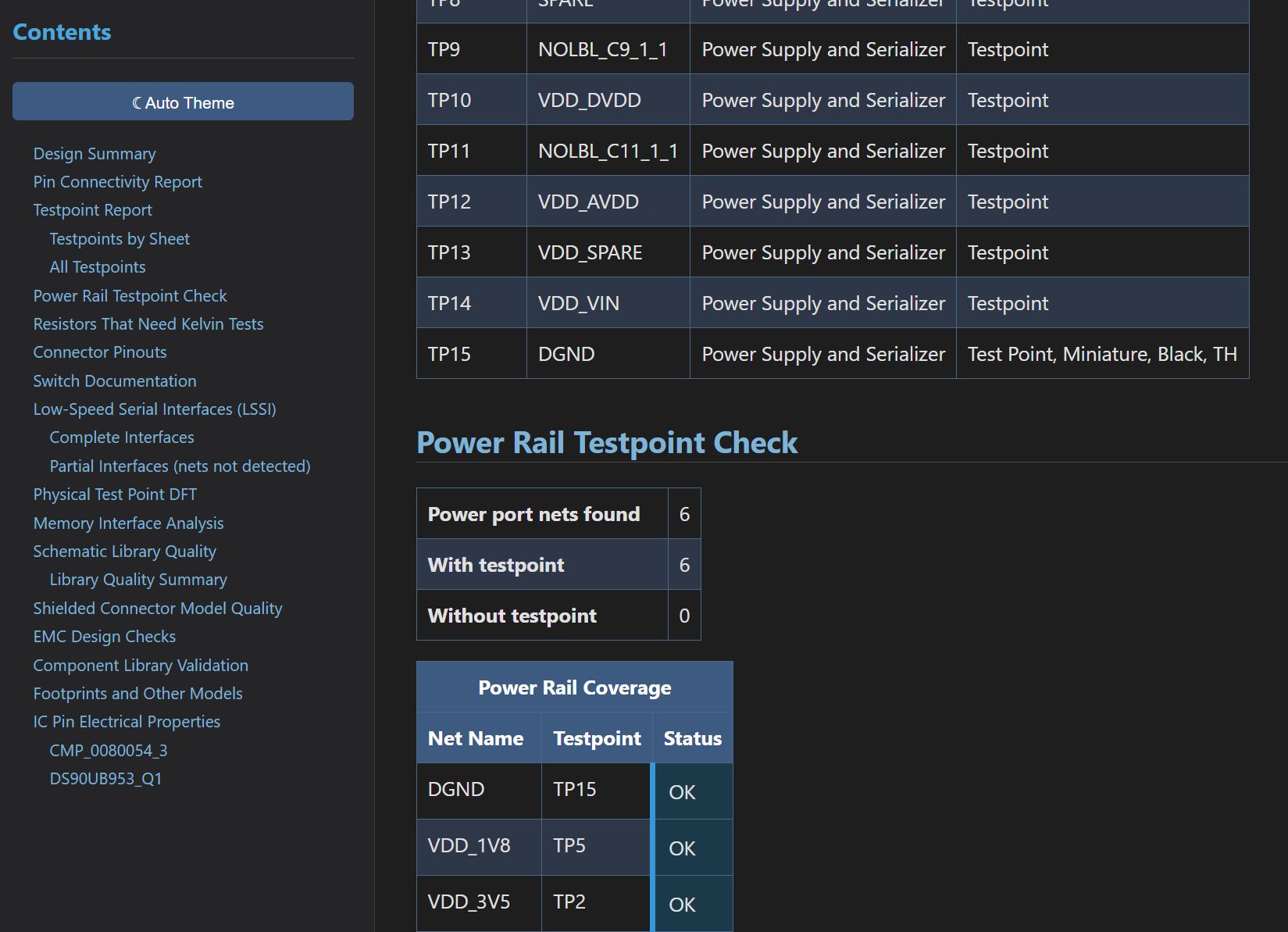

Inventario de puntos de prueba con análisis de cobertura de rieles de alimentación — cada red de alimentación verificada para acceso de prueba.

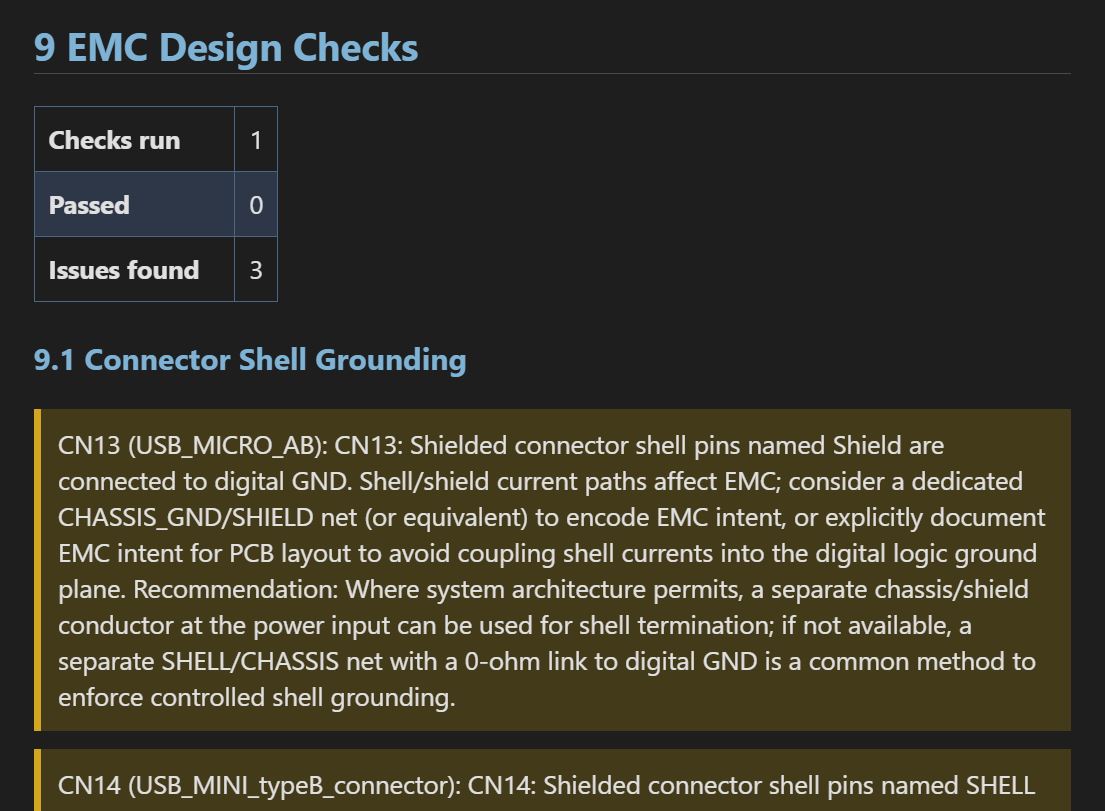

Verificaciones de diseño EMC, validación de biblioteca de componentes y auditoría de footprint/modelo — todo en un solo informe.

El panel de navegación izquierdo le permite saltar directamente a cualquier sección. Los informes incluyen Resumen de Diseño, Conectividad de Pines, Interfaces de Memoria, Interfaces Seriales, Pines de Conectores, Análisis DFT, calificaciones de Calidad de Biblioteca, y más.

Enfoque Actual: Diseños digitales y de señal mixta — procesadores, FPGAs, interfaces de memoria, buses seriales y análisis de testabilidad. Las verificaciones específicas de analógico (estabilidad de lazo de fuente de alimentación, análisis de filtros) están en la hoja de ruta.

Qué Cargar

Comprima sus archivos de esquemático en ZIP y cargue. Esto es lo que necesitamos:

Archivos de esquemático (obligatorio)

Archivos Altium .SchDoc o KiCad .kicad_sch — incluya todas las hojas referenciadas por la jerarquía.

Archivos de proyecto (recomendado)

Altium: .PrjPcb, .PrjPcbStructure, .PrjPcbVariants. KiCad: .kicad_pro. Estos nos indican la jerarquía y la hoja de nivel superior. Sin ellos, deberá especificar el nombre de la hoja superior, o asumiremos un diseño plano.

Archivos *.bsdl (opcional)

Archivos de Descripción de Boundary Scan. Estos archivos usan IEEE 1149.1-2013 para describir la capacidad de prueba de los circuitos integrados digitales. Si se proporcionan, Tomachie analizará la corrección, cumplimiento y Design-for-Test de su diseño.

Consejo: Al solicitar esquemáticos a un diseñador o contratista, pida los archivos de proyecto (.PrjPcb o .kicad_pro) junto con los archivos de esquemático. Muchos diseñadores olvidan incluirlos.