設計レビュードキュメントのサンプル

Standard ERC looks at nets. Tomachie looks at paths — verifying differential pair integrity and impedance continuity across the entire signal chain, even through passive components and connectors. It finds what's hidden: mischaracterized pins, broken impedance paths, and invisible property errors that break your layout wizards. These pre-generated reports show the full analysis output, each containing 10,000+ words of DFT analysis, EMC checks, PCOLA-SOQ scoring, connector pinouts, and testpoint coverage documentation:

- FPGA1394V3 設計レビュー — Xilinx XC7Z020 FPGAを使用したIEEE 1394 FireWireインターフェース、BSDL境界スキャン分析、JTAGチェーン検証

- MB1191 設計レビュー — ARM Cortex-Mプロセッサ搭載STM32 Nucleo-144開発ボード

- TIDA-050036 設計レビュー — Texas Instruments産業用ベースボードリファレンス設計

お試し可能なサンプル

- FPGA1394V3.zip — Xilinx FPGAを使用したIEEE 1394 FireWireインターフェース、マルチシート階層構造

- MB1191.zip — STM32 Nucleo-144開発ボード(ST Microelectronics)

- TIDA-050036.zip — Texas Instruments産業用ベースボードリファレンス設計

サンプルをダウンロードし、提出ページでアップロードすると完全な分析レポートが届きます。

サンプルレポート出力

Tomachieはナビゲーション可能なセクションを持つインタラクティブなHTMLレポートを生成します。お届けする内容は以下の通りです:

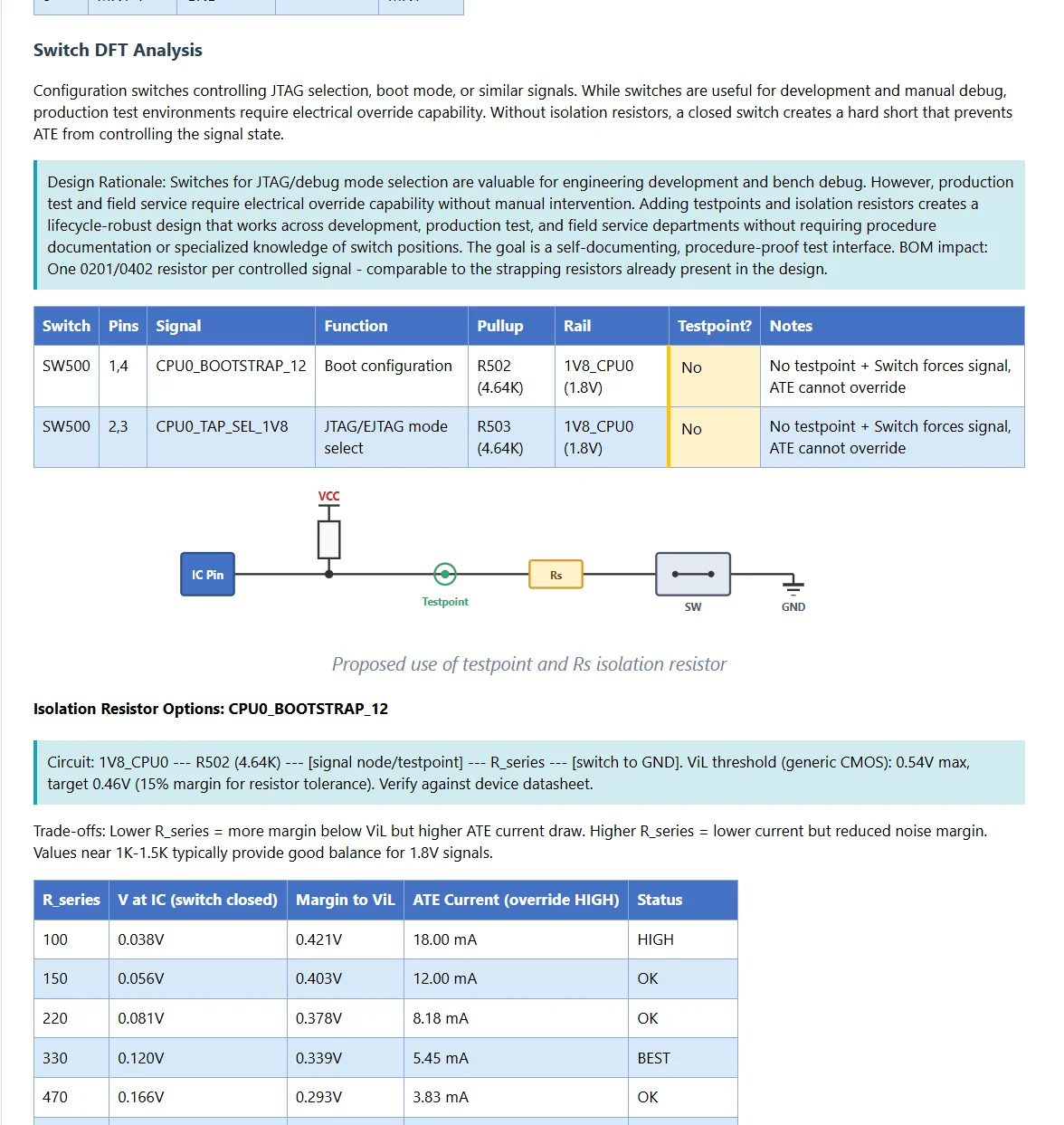

スイッチDFT分析 — テストオーバーライド機能のない設定スイッチを特定し、ATE互換性のためのアイソレーション抵抗値を計算します。

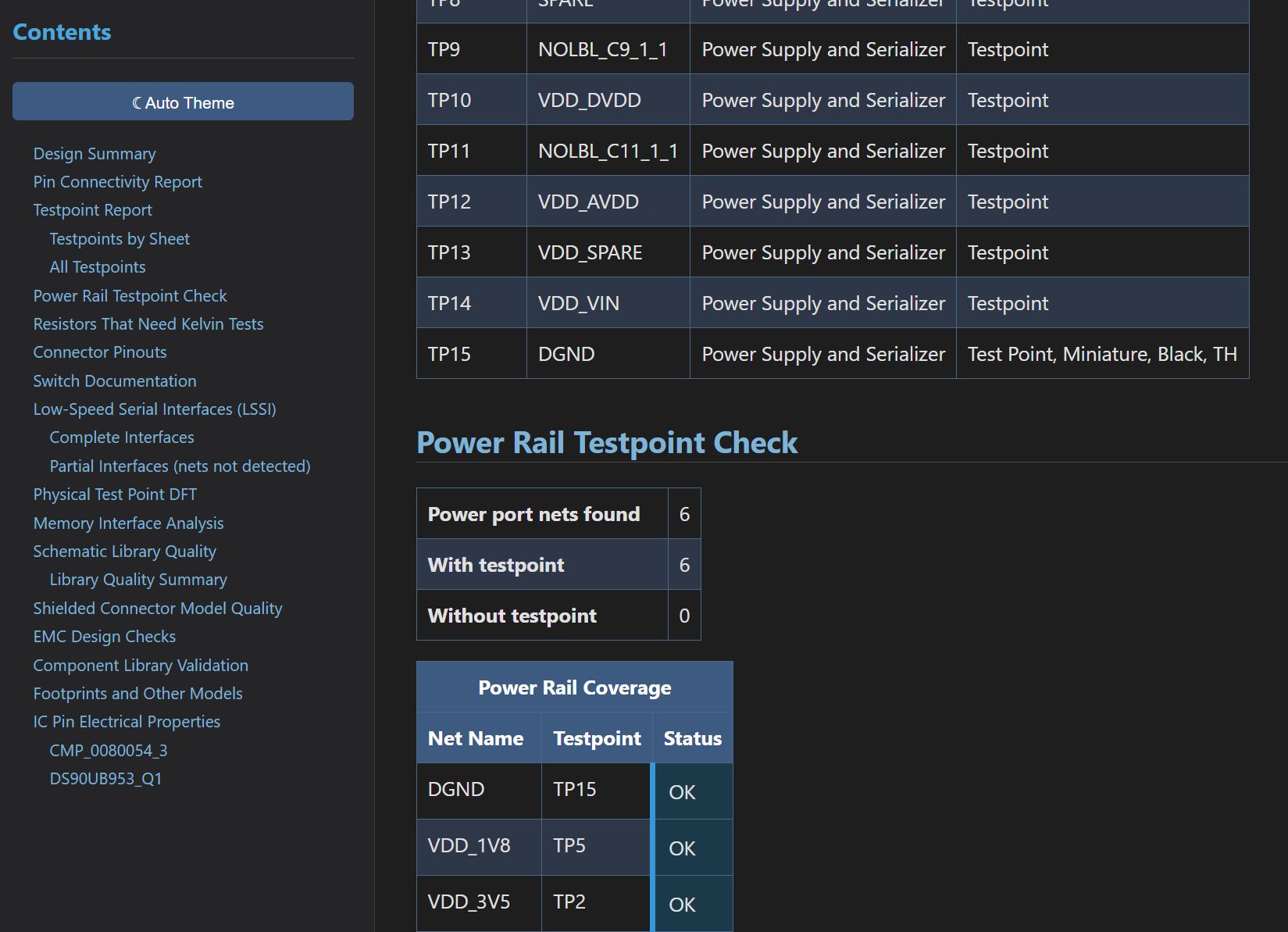

電源レールカバレッジ分析付きテストポイントインベントリ — 全電源ネットのテストアクセスを確認します。

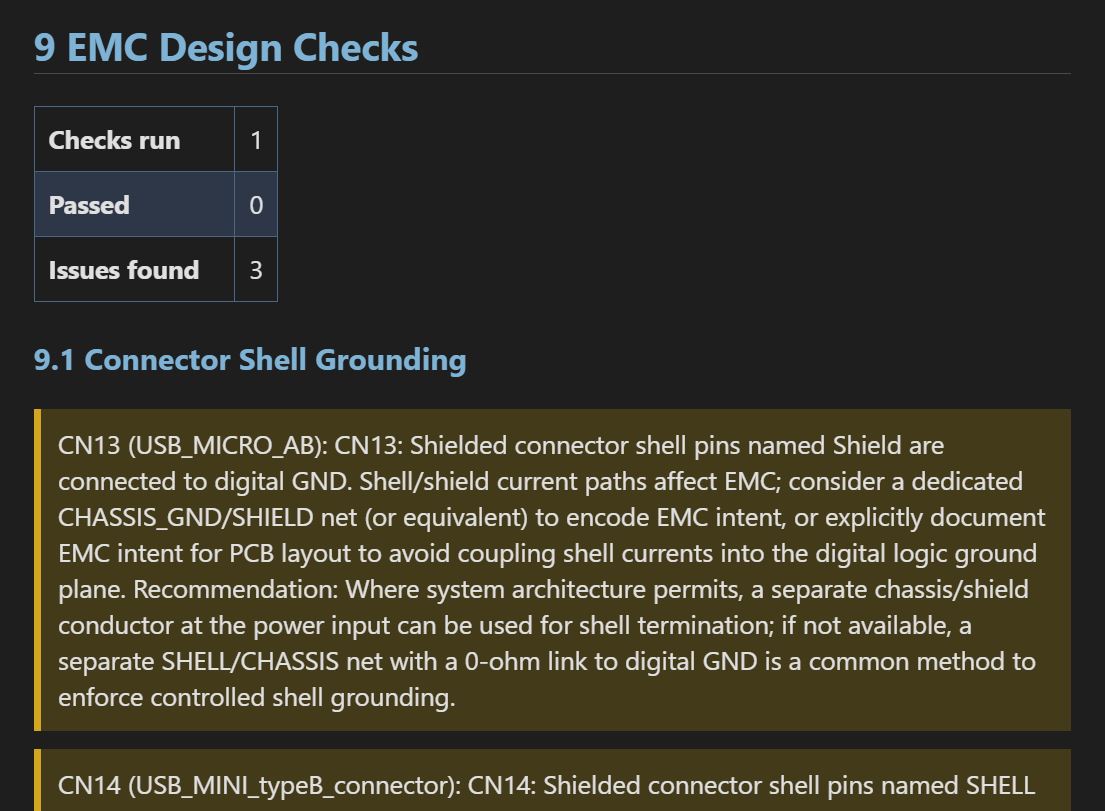

EMC設計チェック、コンポーネントライブラリ検証、フットプリント/モデル監査 — すべてを1つのレポートにまとめました。

左側のナビゲーションパネルから任意のセクションに直接ジャンプできます。レポートには設計サマリー、ピン接続、メモリインターフェース、シリアルインターフェース、コネクタピンアウト、DFT分析、ライブラリ品質グレードなどが含まれます。

現在の対象: デジタルおよびミックスドシグナル設計 — プロセッサ、FPGA、メモリインターフェース、シリアルバス、テスタビリティ分析。アナログ固有のチェック(電源ループ安定性、フィルタ分析)はロードマップに含まれています。

アップロードするもの

回路図ファイルをZIP圧縮してアップロードしてください。必要なものは以下の通りです:

回路図ファイル (必須)

Altium .SchDocまたはKiCad .kicad_schファイル — 階層から参照される全シートを含めてください。

プロジェクトファイル (推奨)

Altium:.PrjPcb、.PrjPcbStructure、.PrjPcbVariants。KiCad:.kicad_pro。これらは階層構造とトップレベルシートを示します。これらがない場合はトップシート名を指定する必要があり、指定がなければフラット設計として扱います。

*.bsdlファイル (任意)

境界スキャン記述言語ファイル。これらのファイルはIEEE 1149.1-2013を使用してデジタルICのテスト機能を記述します。提供された場合、Tomachieは設計の正確性、準拠性、テスト容易性を分析します。

ヒント: 設計者や外注先に回路図を依頼する際は、回路図ファイルとともにプロジェクトファイル(.PrjPcbまたは.kicad_pro)も依頼してください。多くの設計者がこれらを含めるのを忘れがちです。