Примеры документов анализа проекта

Standard ERC looks at nets. Tomachie looks at paths — verifying differential pair integrity and impedance continuity across the entire signal chain, even through passive components and connectors. It finds what's hidden: mischaracterized pins, broken impedance paths, and invisible property errors that break your layout wizards. These pre-generated reports show the full analysis output, each containing 10,000+ words of DFT analysis, EMC checks, PCOLA-SOQ scoring, connector pinouts, and testpoint coverage documentation:

- Обзор проекта FPGA1394V3 — Интерфейс IEEE 1394 FireWire с Xilinx XC7Z020 FPGA, анализ граничного сканирования BSDL, валидация цепочки JTAG

- Обзор проекта MB1191 — Отладочная плата STM32 Nucleo-144 с процессором ARM Cortex-M

- Обзор проекта TIDA-050036 — Эталонный проект промышленной базовой платы Texas Instruments

Примеры для самостоятельной проверки

- FPGA1394V3.zip — Интерфейс IEEE 1394 FireWire с Xilinx FPGA, многолистовая иерархия

- MB1191.zip — Отладочная плата STM32 Nucleo-144 (ST Microelectronics)

- TIDA-050036.zip — Эталонный проект промышленной базовой платы Texas Instruments

Скачайте любой пример, загрузите его на странице «Отправить» и получите полный аналитический отчёт.

Пример содержания отчёта

Tomachie генерирует интерактивный HTML-отчёт с навигацией по разделам. Вот что вы получите:

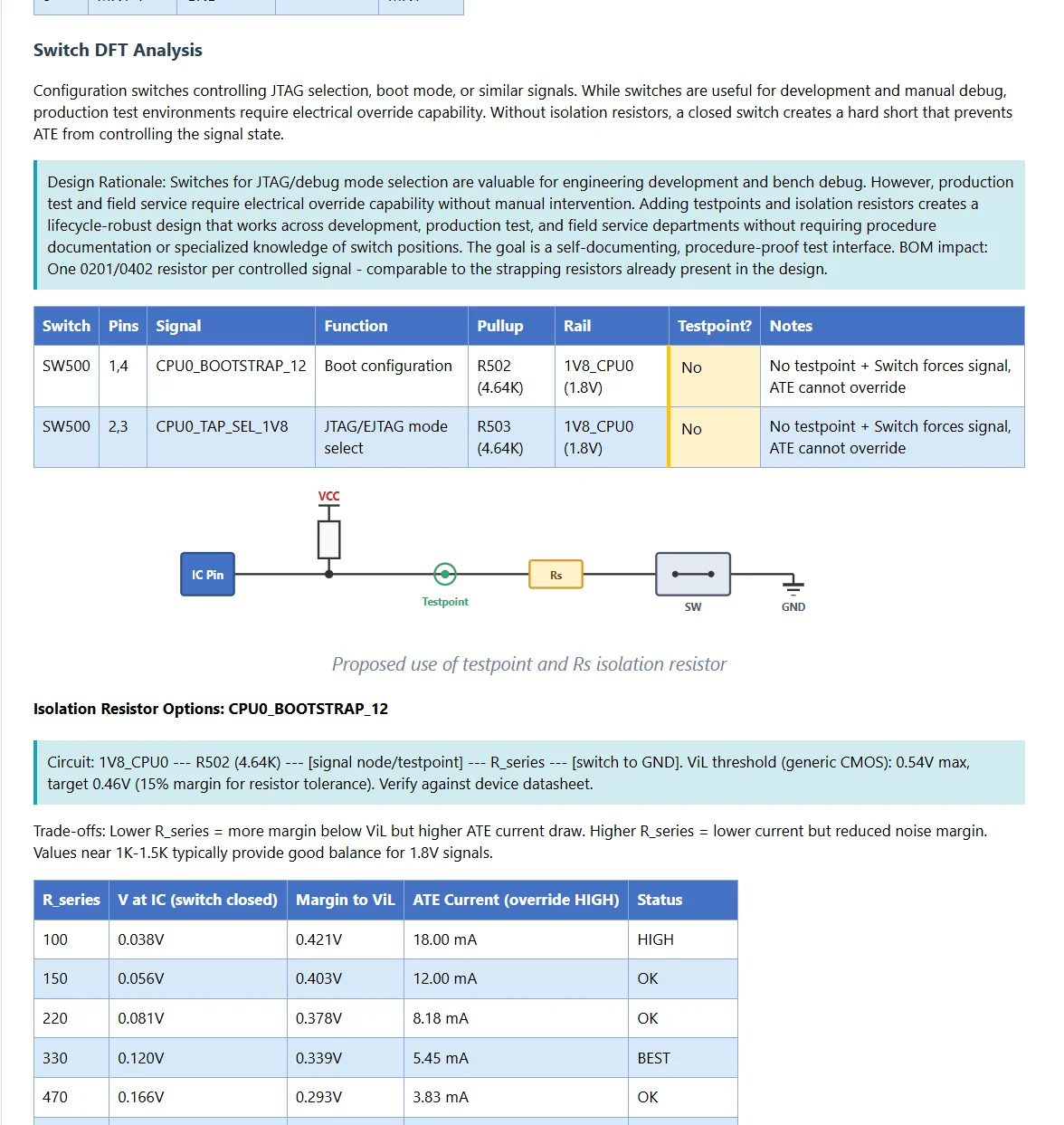

DFT-анализ переключателей — выявляет конфигурационные переключатели без возможности тестового управления, рассчитывает значения изоляционных резисторов для совместимости с ATE.

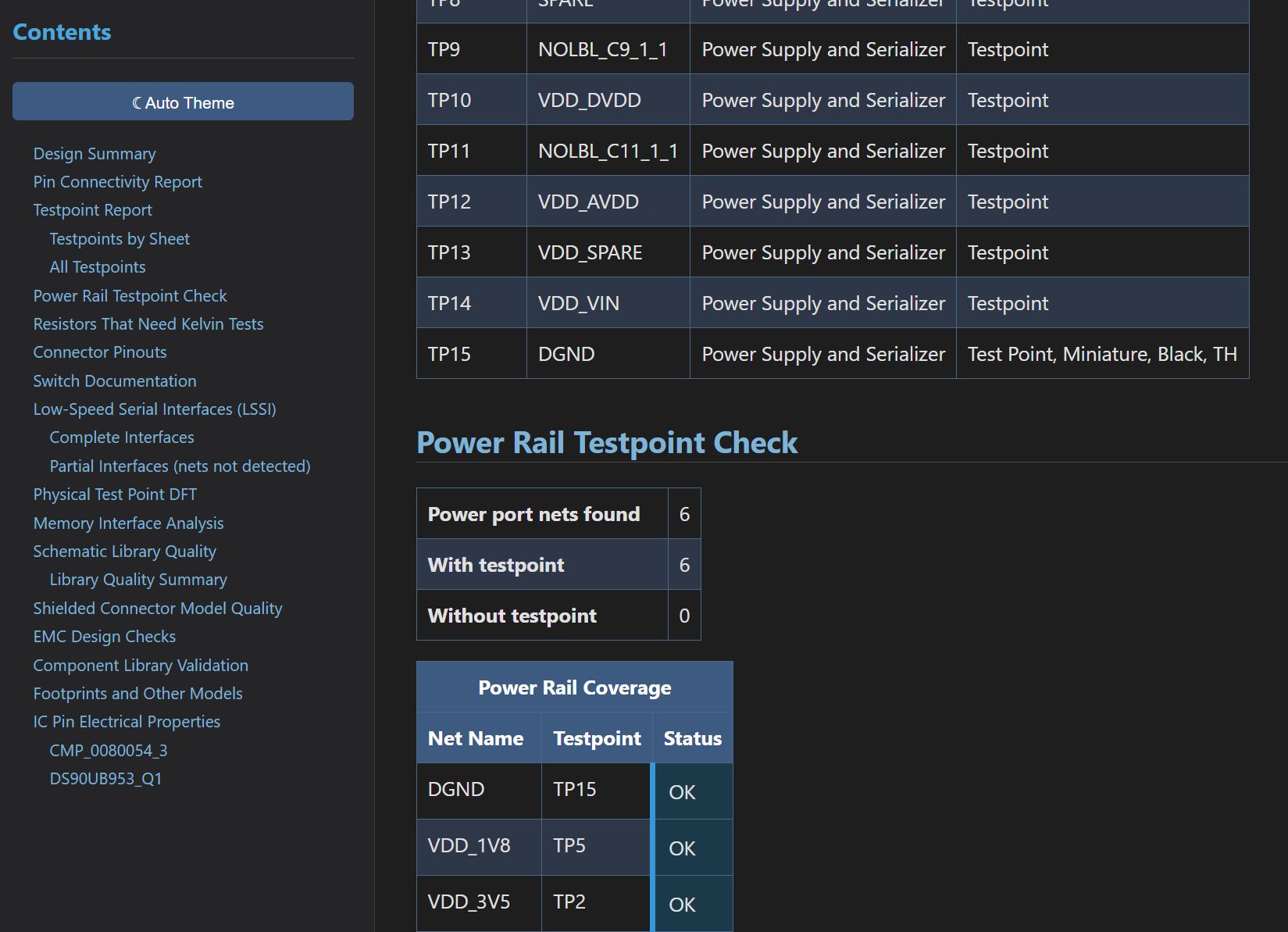

Инвентаризация тестовых точек с анализом покрытия шин питания — каждая силовая цепь проверена на наличие тестового доступа.

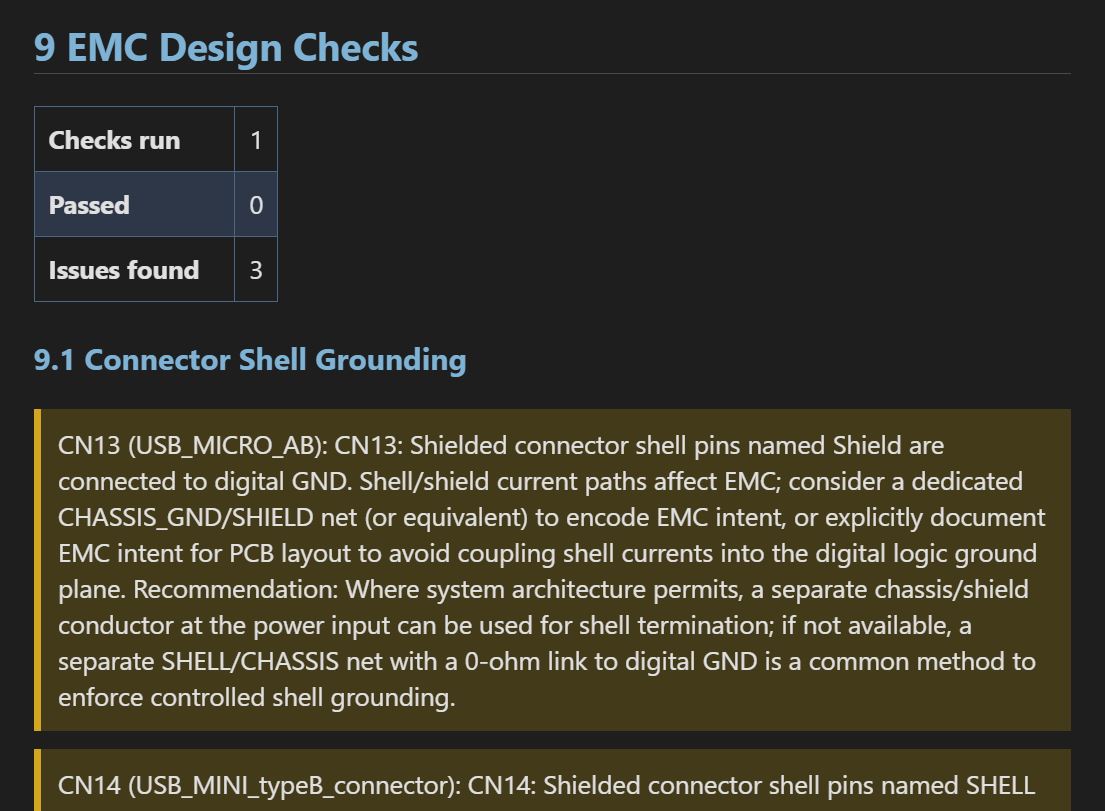

Проверки ЭМС, валидация библиотек компонентов, аудит посадочных мест и моделей — всё в одном отчёте.

Левая навигационная панель позволяет перейти к любому разделу. Отчёты включают: общие сведения о проекте, связность выводов, интерфейсы памяти, последовательные интерфейсы, распиновку разъёмов, DFT-анализ, оценки качества библиотек и многое другое.

Текущая специализация: Цифровые и смешанные проекты — процессоры, FPGA, интерфейсы памяти, последовательные шины и анализ тестируемости. Проверки, специфичные для аналоговых схем (устойчивость контуров питания, анализ фильтров), запланированы на будущее.

Что загружать

Заархивируйте файлы схемы в ZIP и загрузите. Вот что нам нужно:

Файлы схемы (обязательно)

Файлы Altium .SchDoc или KiCad .kicad_sch — включите все листы, на которые ссылается иерархия.

Файлы проекта (рекомендуется)

Altium: .PrjPcb, .PrjPcbStructure, .PrjPcbVariants. KiCad: .kicad_pro. Они определяют иерархию и лист верхнего уровня. Без них потребуется указать имя верхнего листа, иначе мы предположим плоскую структуру.

Файлы *.bsdl (необязательно)

Файлы описания граничного сканирования (Boundary Scan Description Language). Эти файлы используют IEEE 1149.1-2013 для описания тестовых возможностей цифровых ИС. При их наличии Tomachie проанализирует корректность, соответствие стандартам и тестируемость вашего проекта.

Совет: При запросе схем у проектировщика или подрядчика попросите также файлы проекта (.PrjPcb или .kicad_pro) вместе с файлами схемы. Многие проектировщики забывают их включить.