Tài liệu đánh giá thiết kế mẫu

Standard ERC looks at nets. Tomachie looks at paths — verifying differential pair integrity and impedance continuity across the entire signal chain, even through passive components and connectors. It finds what's hidden: mischaracterized pins, broken impedance paths, and invisible property errors that break your layout wizards. These pre-generated reports show the full analysis output, each containing 10,000+ words of DFT analysis, EMC checks, PCOLA-SOQ scoring, connector pinouts, and testpoint coverage documentation:

- Đánh giá thiết kế FPGA1394V3 — Giao diện IEEE 1394 FireWire với Xilinx XC7Z020 FPGA, phân tích boundary scan BSDL, xác thực chuỗi JTAG

- Đánh giá thiết kế MB1191 — Bo mạch phát triển STM32 Nucleo-144 với bộ xử lý ARM Cortex-M

- Đánh giá thiết kế TIDA-050036 — Thiết kế tham chiếu bo mạch công nghiệp Texas Instruments

Mẫu bạn có thể thử

- FPGA1394V3.zip — Giao diện IEEE 1394 FireWire với Xilinx FPGA, phân cấp nhiều trang

- MB1191.zip — Bo mạch phát triển STM32 Nucleo-144 (ST Microelectronics)

- TIDA-050036.zip — Thiết kế tham chiếu bo mạch công nghiệp Texas Instruments

Tải xuống bất kỳ mẫu nào, tải lên trên trang Gửi và nhận báo cáo phân tích đầy đủ.

Đầu ra báo cáo mẫu

Tomachie tạo báo cáo HTML tương tác với các phần có thể điều hướng. Đây là những gì bạn sẽ nhận được:

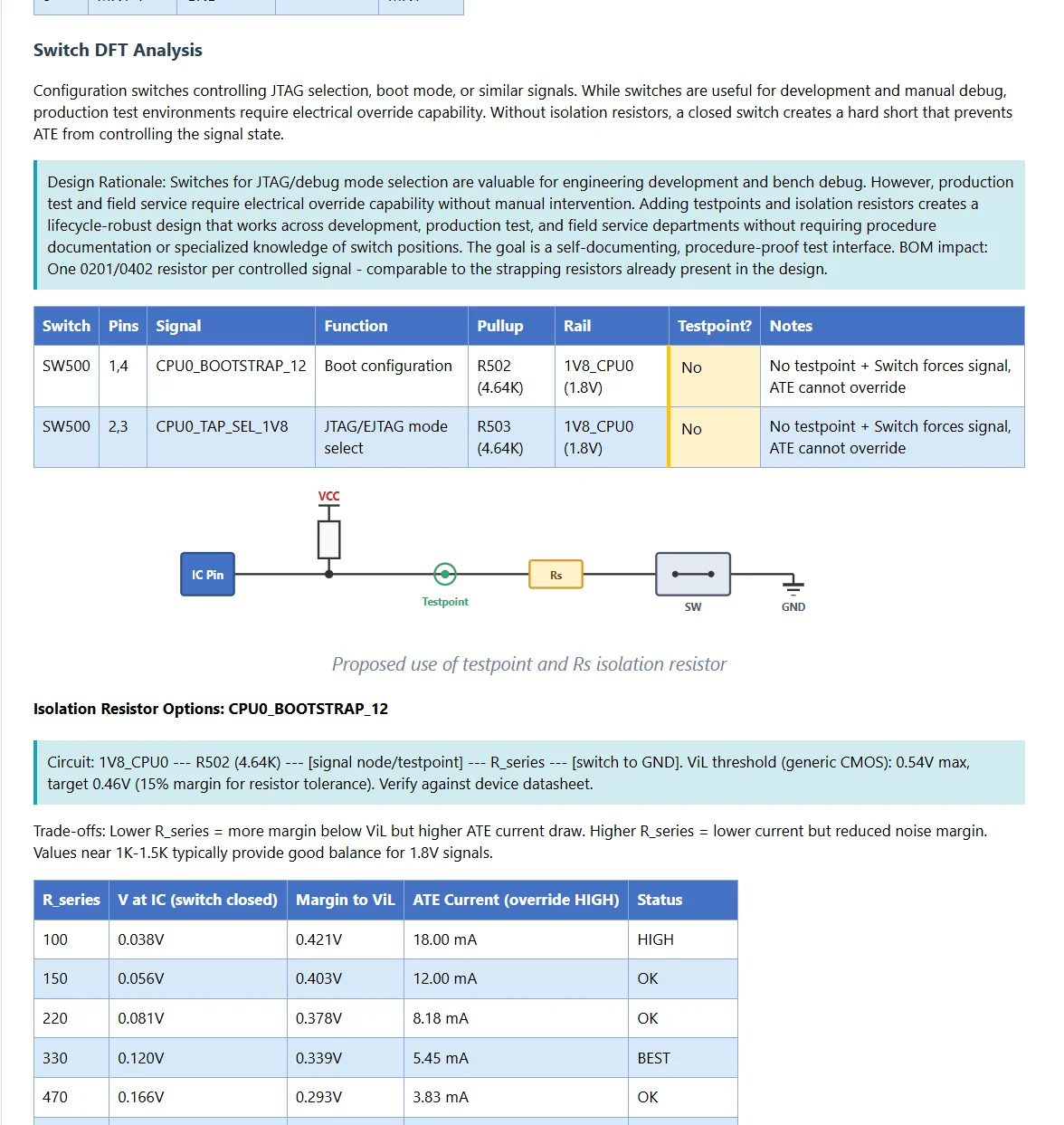

Phân tích DFT công tắc — xác định công tắc cấu hình thiếu khả năng ghi đè kiểm tra, tính toán giá trị điện trở cách ly cho tương thích ATE.

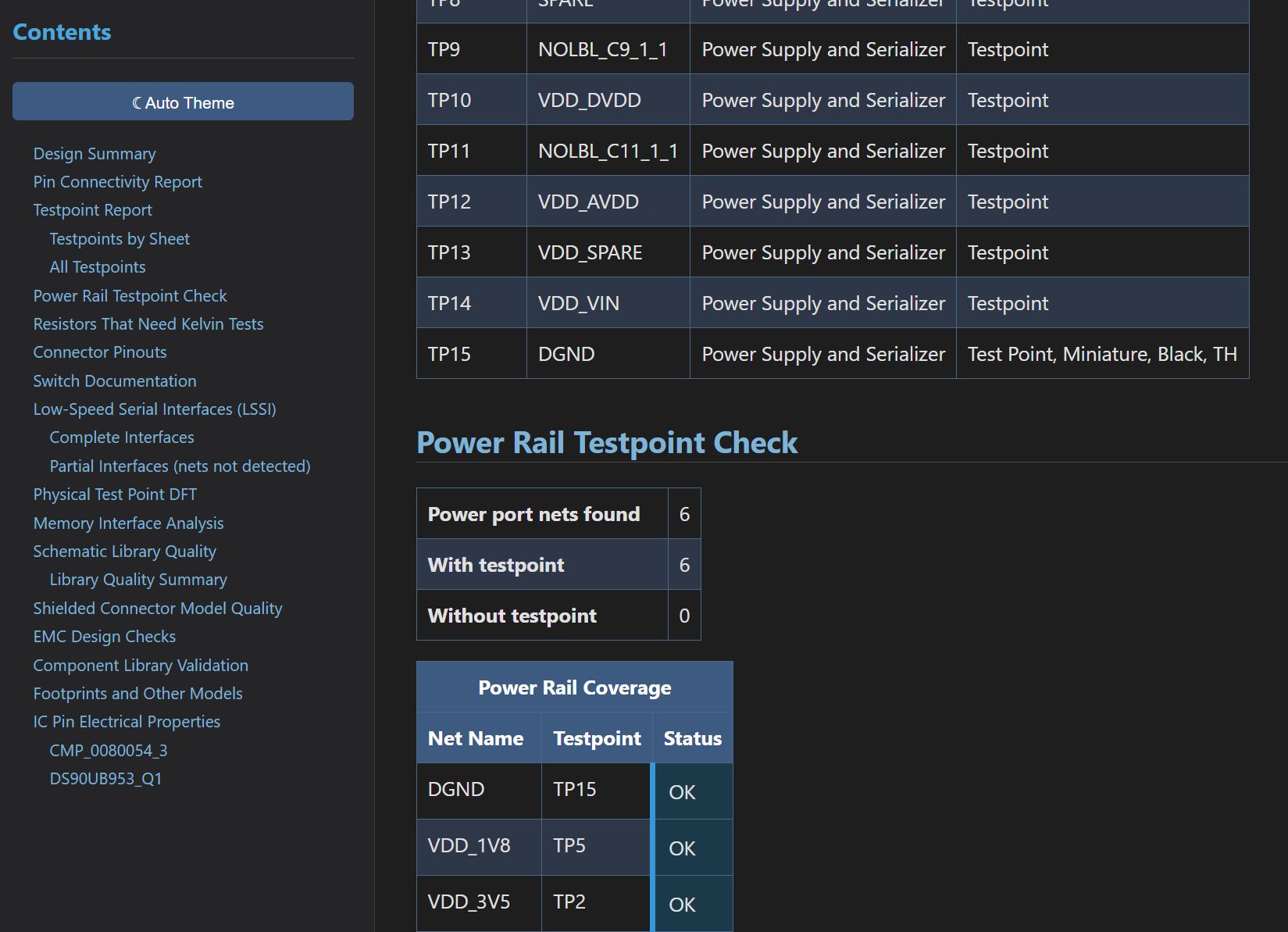

Kiểm kê điểm kiểm tra với phân tích phủ đường nguồn — mọi net nguồn đều được kiểm tra truy cập kiểm tra.

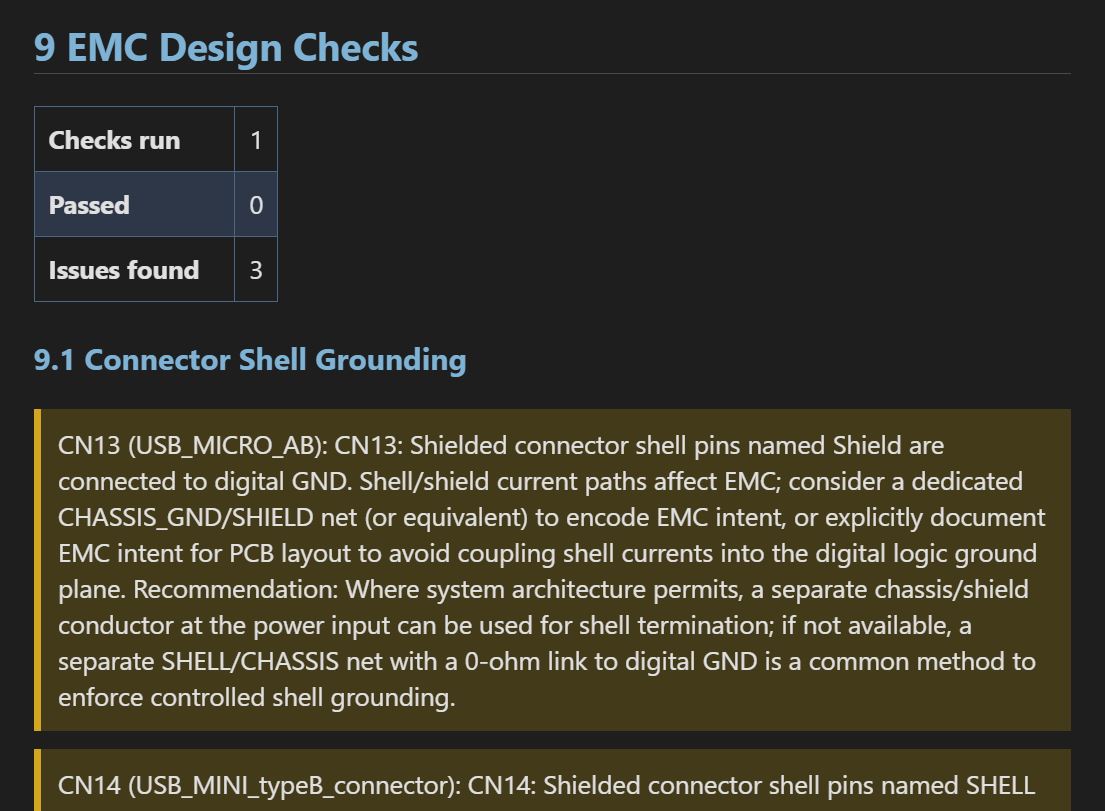

Kiểm tra thiết kế EMC, xác thực thư viện linh kiện và kiểm tra footprint/mô hình — tất cả trong một báo cáo.

Bảng điều hướng bên trái cho phép nhảy trực tiếp đến bất kỳ phần nào. Báo cáo bao gồm Tóm tắt thiết kế, Kết nối chân, Giao diện bộ nhớ, Giao diện nối tiếp, Chân kết nối, Phân tích DFT, Xếp hạng chất lượng thư viện và nhiều hơn nữa.

Trọng tâm hiện tại: Thiết kế kỹ thuật số và tín hiệu hỗn hợp — bộ xử lý, FPGA, giao diện bộ nhớ, bus nối tiếp và phân tích khả năng kiểm tra. Kiểm tra chuyên biệt analog (ổn định vòng nguồn, phân tích bộ lọc) đang trong lộ trình phát triển.

Nội dung cần tải lên

Nén tệp sơ đồ nguyên lý thành ZIP và tải lên. Đây là những gì chúng tôi cần:

Tệp sơ đồ nguyên lý (bắt buộc)

Tệp Altium .SchDoc hoặc KiCad .kicad_sch — bao gồm tất cả trang được tham chiếu bởi phân cấp.

Tệp dự án (khuyến nghị)

Altium: .PrjPcb, .PrjPcbStructure, .PrjPcbVariants. KiCad: .kicad_pro. Các tệp này cho biết phân cấp và trang cấp cao nhất. Nếu không có, bạn cần chỉ định tên trang cấp cao nhất, hoặc chúng tôi sẽ giả định thiết kế phẳng.

Tệp *.bsdl (tùy chọn)

Tệp Boundary Scan Description Language. Các tệp này sử dụng IEEE 1149.1-2013 để mô tả khả năng kiểm tra của IC số. Nếu được cung cấp, Tomachie sẽ phân tích tính đúng đắn, tuân thủ và DFT của thiết kế.

Mẹo: Khi yêu cầu sơ đồ nguyên lý từ nhà thiết kế hoặc nhà thầu, hãy yêu cầu tệp dự án (.PrjPcb hoặc .kicad_pro) cùng với tệp sơ đồ. Nhiều nhà thiết kế quên bao gồm chúng.