设计审查文档示例

Standard ERC looks at nets. Tomachie looks at paths — verifying differential pair integrity and impedance continuity across the entire signal chain, even through passive components and connectors. It finds what's hidden: mischaracterized pins, broken impedance paths, and invisible property errors that break your layout wizards. These pre-generated reports show the full analysis output, each containing 10,000+ words of DFT analysis, EMC checks, PCOLA-SOQ scoring, connector pinouts, and testpoint coverage documentation:

- FPGA1394V3设计审查 — IEEE 1394 FireWire接口,配备Xilinx XC7Z020 FPGA,BSDL边界扫描分析,JTAG链验证

- MB1191设计审查 — STM32 Nucleo-144开发板,配备ARM Cortex-M处理器

- TIDA-050036设计审查 — Texas Instruments工业基板参考设计

可供试用的样例

- FPGA1394V3.zip — IEEE 1394 FireWire接口,配备Xilinx FPGA,多层级原理图

- MB1191.zip — STM32 Nucleo-144开发板(ST Microelectronics)

- TIDA-050036.zip — Texas Instruments工业基板参考设计

下载任意样例,在提交页面上传,即可获得完整的分析报告。

报告输出示例

Tomachie生成带有可导航章节的交互式HTML报告。以下是您将收到的内容:

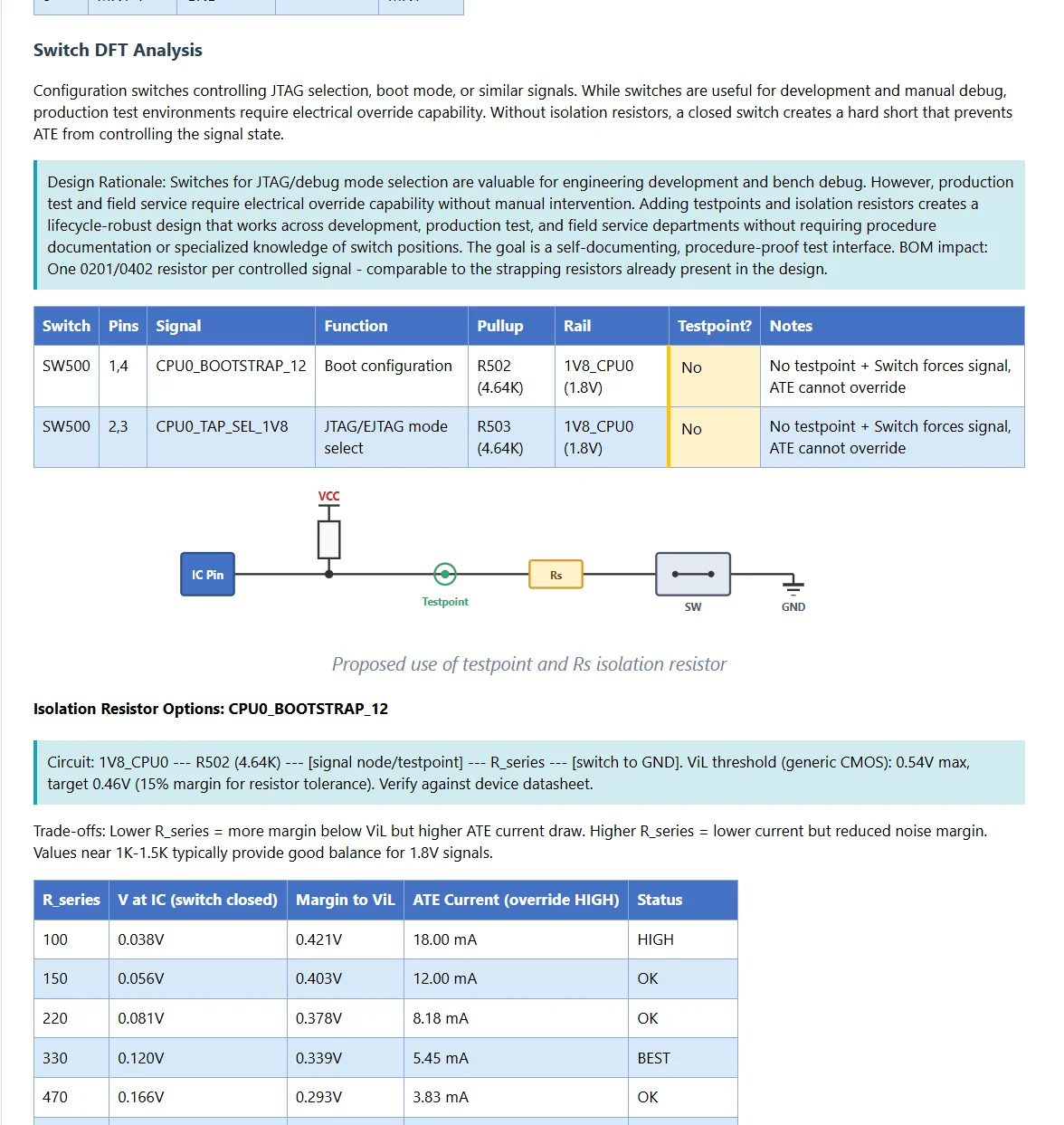

Switch DFT分析——识别缺少测试覆盖能力的配置开关,计算ATE兼容性隔离电阻值。

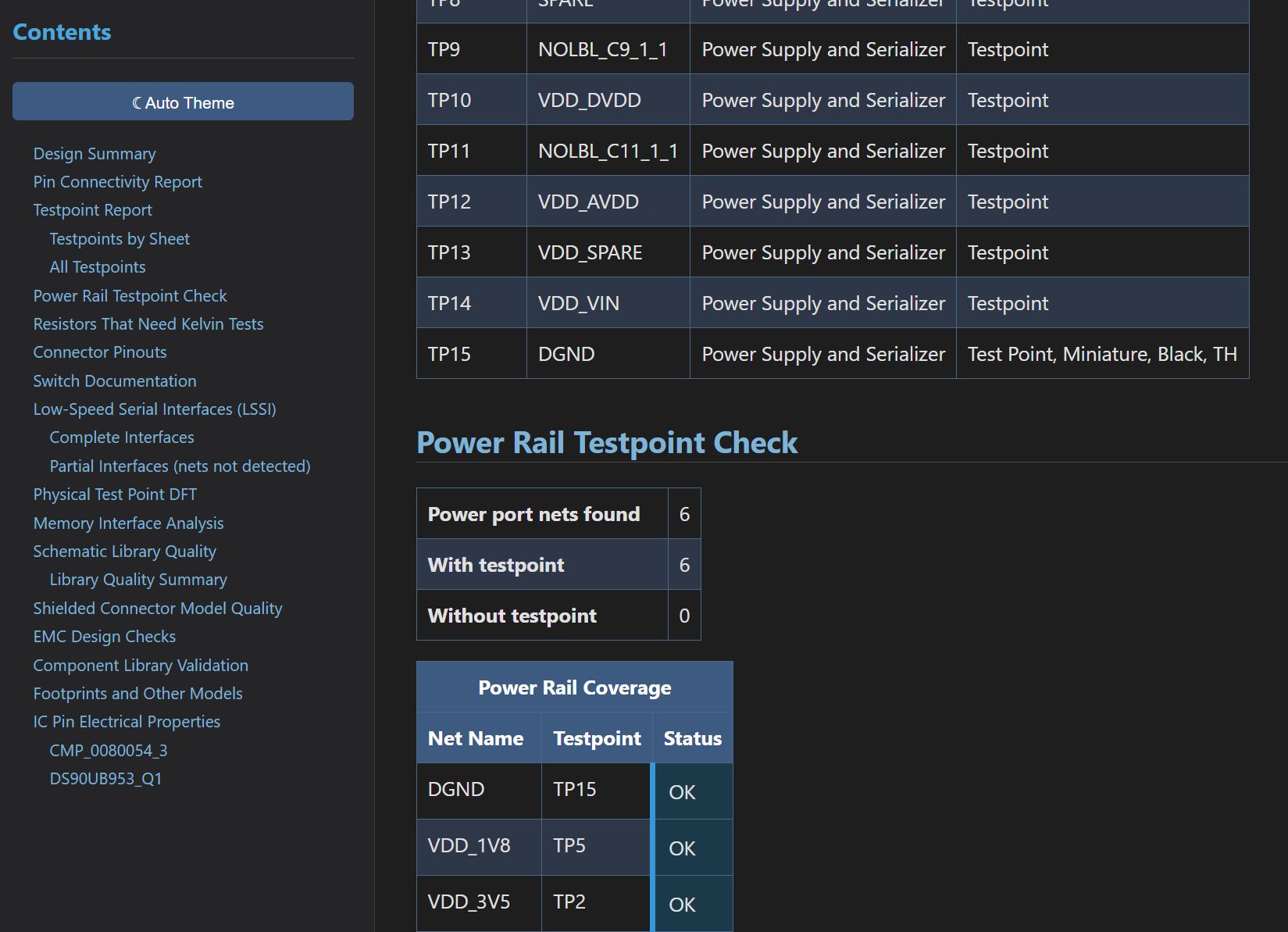

测试点清单与电源轨覆盖分析——检查每个电源网络的测试接入。

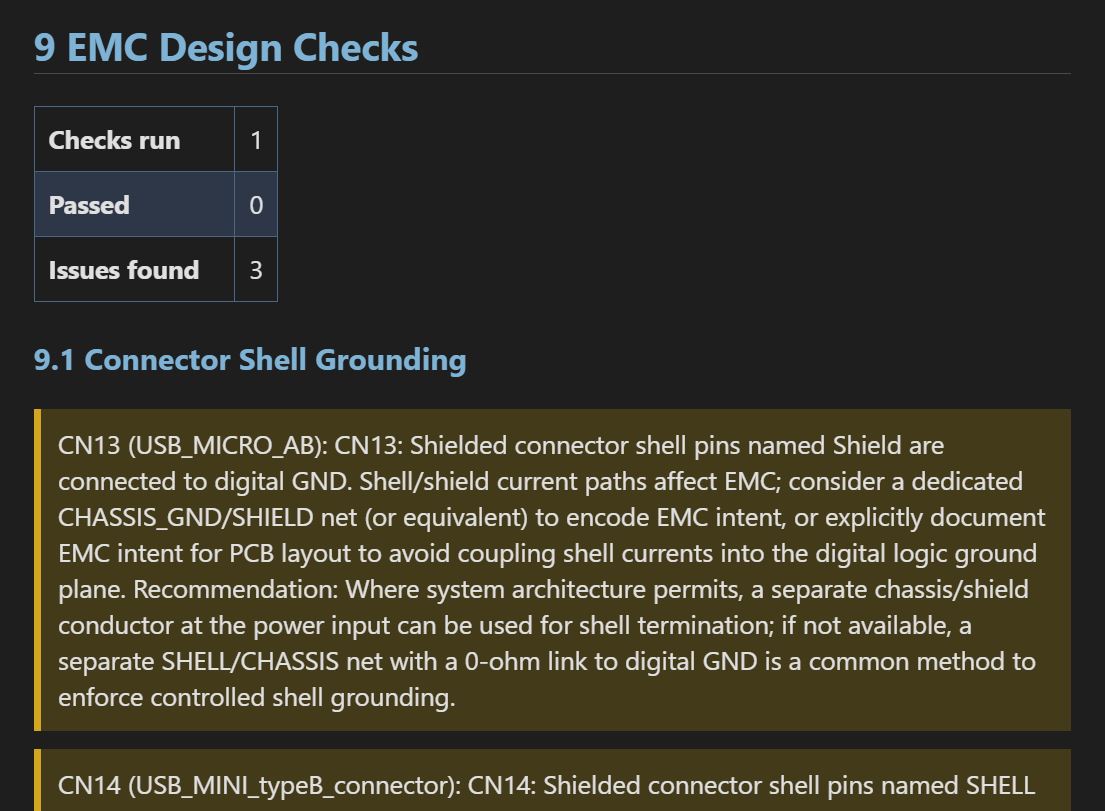

EMC设计检查、元件库验证和封装/模型审计——全部集成在一份报告中。

左侧导航面板可让您直接跳转到任意章节。报告包括设计摘要、引脚连通性、存储器接口、串行接口、连接器引脚分配、DFT分析、元件库质量等级等内容。

当前重点: 数字和混合信号设计——处理器、FPGA、存储器接口、串行总线和可测试性分析。模拟特定检查(电源环路稳定性、滤波器分析)在开发路线图中。

上传内容

将您的原理图文件打包成ZIP并上传。以下是我们需要的内容:

原理图文件 (必需)

Altium .SchDoc或KiCad .kicad_sch文件——请包含层级引用的所有图纸。

项目文件 (推荐)

Altium:.PrjPcb、.PrjPcbStructure、.PrjPcbVariants。KiCad:.kicad_pro。这些文件告诉我们层级结构和顶层图纸。如果没有,您需要指定顶层图纸名称,否则我们将假定为平面设计。

*.bsdl文件 (可选)

边界扫描描述语言文件。这些文件使用IEEE 1149.1-2013来描述数字IC的测试能力。如果提供,Tomachie将分析您设计的正确性、合规性和可测试性设计。

提示: 向设计师或承包商索取原理图时,请要求提供项目文件(.PrjPcb或.kicad_pro)以及原理图文件。许多设计师会忘记包含它们。