Exemples de documents de revue de conception

Standard ERC looks at nets. Tomachie looks at paths — verifying differential pair integrity and impedance continuity across the entire signal chain, even through passive components and connectors. It finds what's hidden: mischaracterized pins, broken impedance paths, and invisible property errors that break your layout wizards. These pre-generated reports show the full analysis output, each containing 10,000+ words of DFT analysis, EMC checks, PCOLA-SOQ scoring, connector pinouts, and testpoint coverage documentation:

- Revue de conception FPGA1394V3 — Interface IEEE 1394 FireWire avec FPGA Xilinx XC7Z020, analyse boundary scan BSDL, validation de chaîne JTAG

- Revue de conception MB1191 — Carte de développement STM32 Nucleo-144 avec processeur ARM Cortex-M

- Revue de conception TIDA-050036 — Conception de référence de carte de base industrielle Texas Instruments

Échantillons à essayer

- FPGA1394V3.zip — Interface IEEE 1394 FireWire avec FPGA Xilinx, hiérarchie multi-feuilles

- MB1191.zip — Carte de développement STM32 Nucleo-144 (ST Microelectronics)

- TIDA-050036.zip — Conception de référence de carte de base industrielle Texas Instruments

Téléchargez n'importe quel échantillon, téléversez-le sur la page Soumettre et recevez un rapport d'analyse complet.

Exemple de rapport généré

Tomachie génère un rapport HTML interactif avec des sections navigables. Voici ce que vous recevrez :

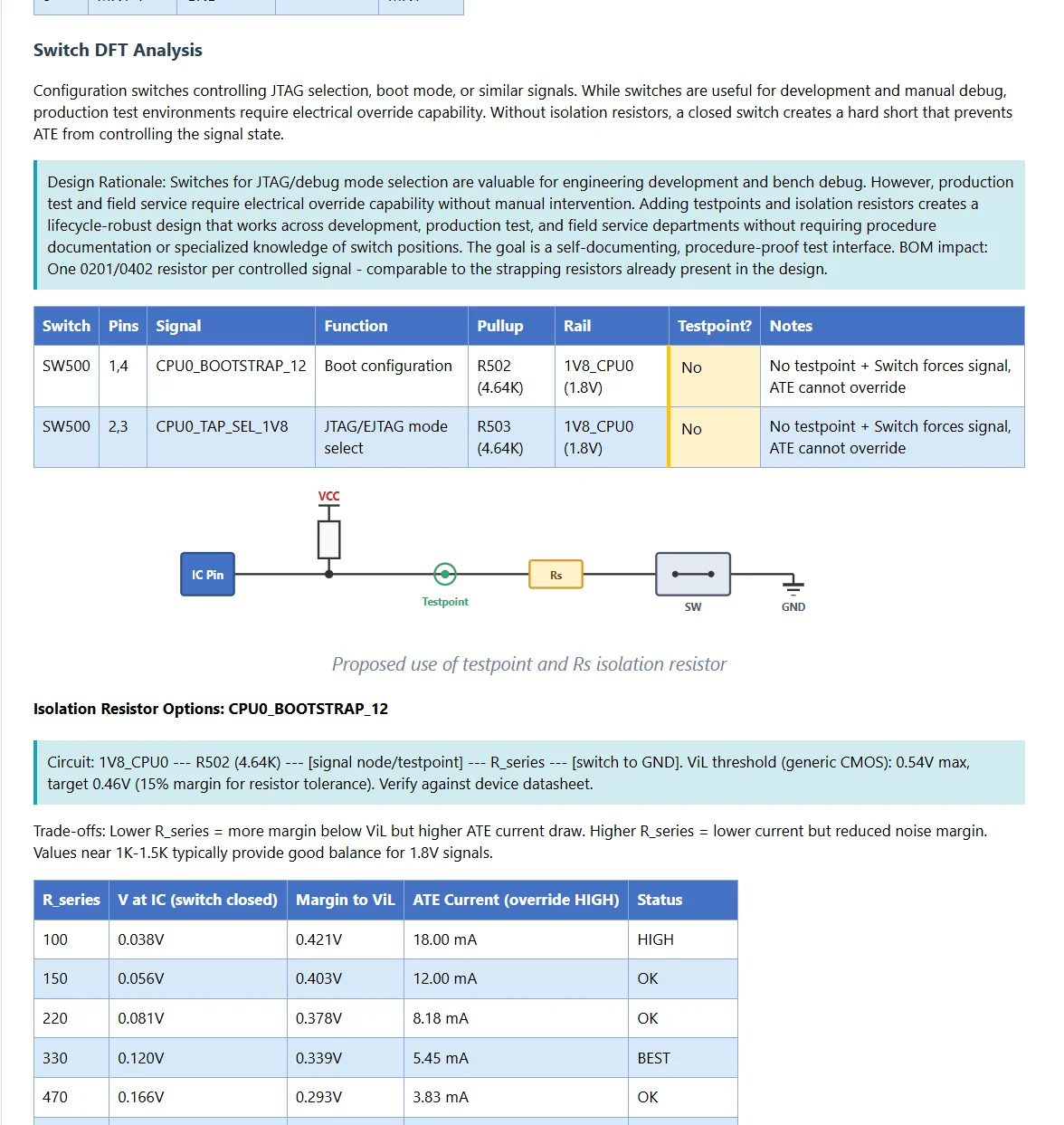

Analyse DFT des commutateurs — identifie les commutateurs de configuration sans capacité de remplacement de test, calcule les valeurs de résistances d'isolation pour la compatibilité ATE.

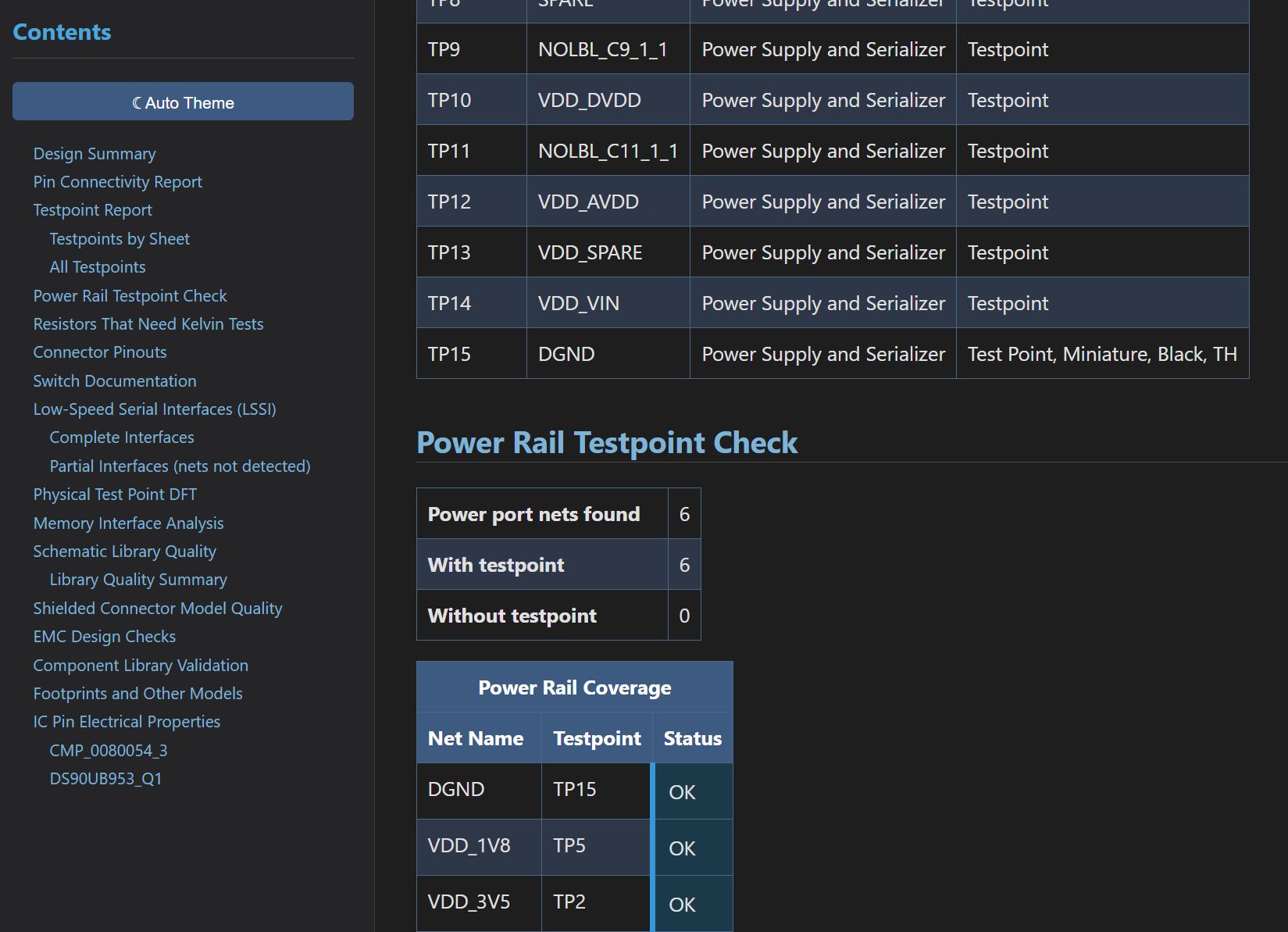

Inventaire des points de test avec analyse de couverture des rails d'alimentation — chaque net d'alimentation vérifié pour l'accès de test.

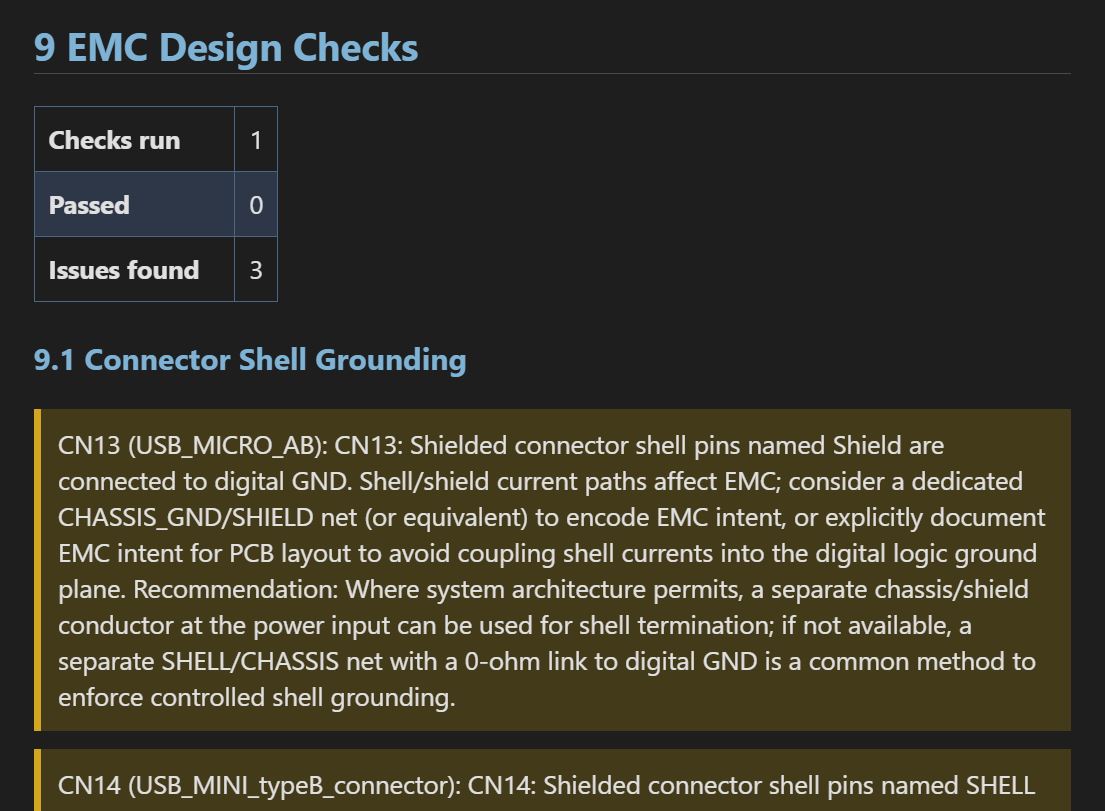

Vérifications CEM de conception, validation de bibliothèque de composants et audit empreinte/modèle — le tout dans un seul rapport.

Le panneau de navigation gauche permet d'accéder directement à n'importe quelle section. Les rapports incluent le résumé de conception, la connectivité des broches, les interfaces mémoire, les interfaces série, le brochage des connecteurs, l'analyse DFT, les évaluations de qualité de bibliothèque, et plus encore.

Focus actuel : Conceptions numériques et mixtes — processeurs, FPGA, interfaces mémoire, bus série et analyse de testabilité. Les vérifications spécifiques à l'analogique (stabilité de boucle d'alimentation, analyse de filtres) sont dans la feuille de route.

Que téléverser

Zippez vos fichiers de schéma et téléversez. Voici ce dont nous avons besoin :

Fichiers de schéma (requis)

Fichiers Altium .SchDoc ou KiCad .kicad_sch — incluez toutes les feuilles référencées par la hiérarchie.

Fichiers de projet (recommandé)

Altium : .PrjPcb, .PrjPcbStructure, .PrjPcbVariants. KiCad : .kicad_pro. Ceux-ci nous indiquent la hiérarchie et la feuille de niveau supérieur. Sans eux, vous devrez spécifier le nom de la feuille supérieure, sinon nous supposerons une conception plate.

Fichiers *.bsdl (facultatif)

Fichiers BSDL (Boundary Scan Description Language). Ces fichiers utilisent la norme IEEE 1149.1-2013 pour décrire la capacité de test des circuits intégrés numériques. S'ils sont fournis, Tomachie analysera la conformité et le Design-for-Test de votre conception.

Conseil : Lorsque vous demandez des schémas à un concepteur ou un sous-traitant, demandez les fichiers de projet (.PrjPcb ou .kicad_pro) en plus des fichiers de schéma. Beaucoup de concepteurs oublient de les inclure.