דוגמאות למסמכי סקירת עיצוב

Standard ERC looks at nets. Tomachie looks at paths — verifying differential pair integrity and impedance continuity across the entire signal chain, even through passive components and connectors. It finds what's hidden: mischaracterized pins, broken impedance paths, and invisible property errors that break your layout wizards. These pre-generated reports show the full analysis output, each containing 10,000+ words of DFT analysis, EMC checks, PCOLA-SOQ scoring, connector pinouts, and testpoint coverage documentation:

- סקירת עיצוב FPGA1394V3 — ממשק IEEE 1394 FireWire עם Xilinx XC7Z020 FPGA, ניתוח boundary scan עם BSDL, אימות שרשרת JTAG

- סקירת עיצוב MB1191 — לוח פיתוח STM32 Nucleo-144 עם מעבד ARM Cortex-M

- סקירת עיצוב TIDA-050036 — עיצוב ייחוס של לוח בסיס תעשייתי מ-Texas Instruments

דגימות לניסוי

- FPGA1394V3.zip — ממשק IEEE 1394 FireWire עם Xilinx FPGA, היררכיה מרובת דפים

- MB1191.zip — לוח פיתוח STM32 Nucleo-144 (ST Microelectronics)

- TIDA-050036.zip — עיצוב ייחוס של לוח בסיס תעשייתי מ-Texas Instruments

הורידו כל דגימה, העלו אותה בדף ההגשה וקבלו דוח ניתוח מלא.

דוגמת פלט דוח

Tomachie מייצר דוח HTML אינטראקטיבי עם מקטעים ניתנים לניווט. הנה מה שתקבלו:

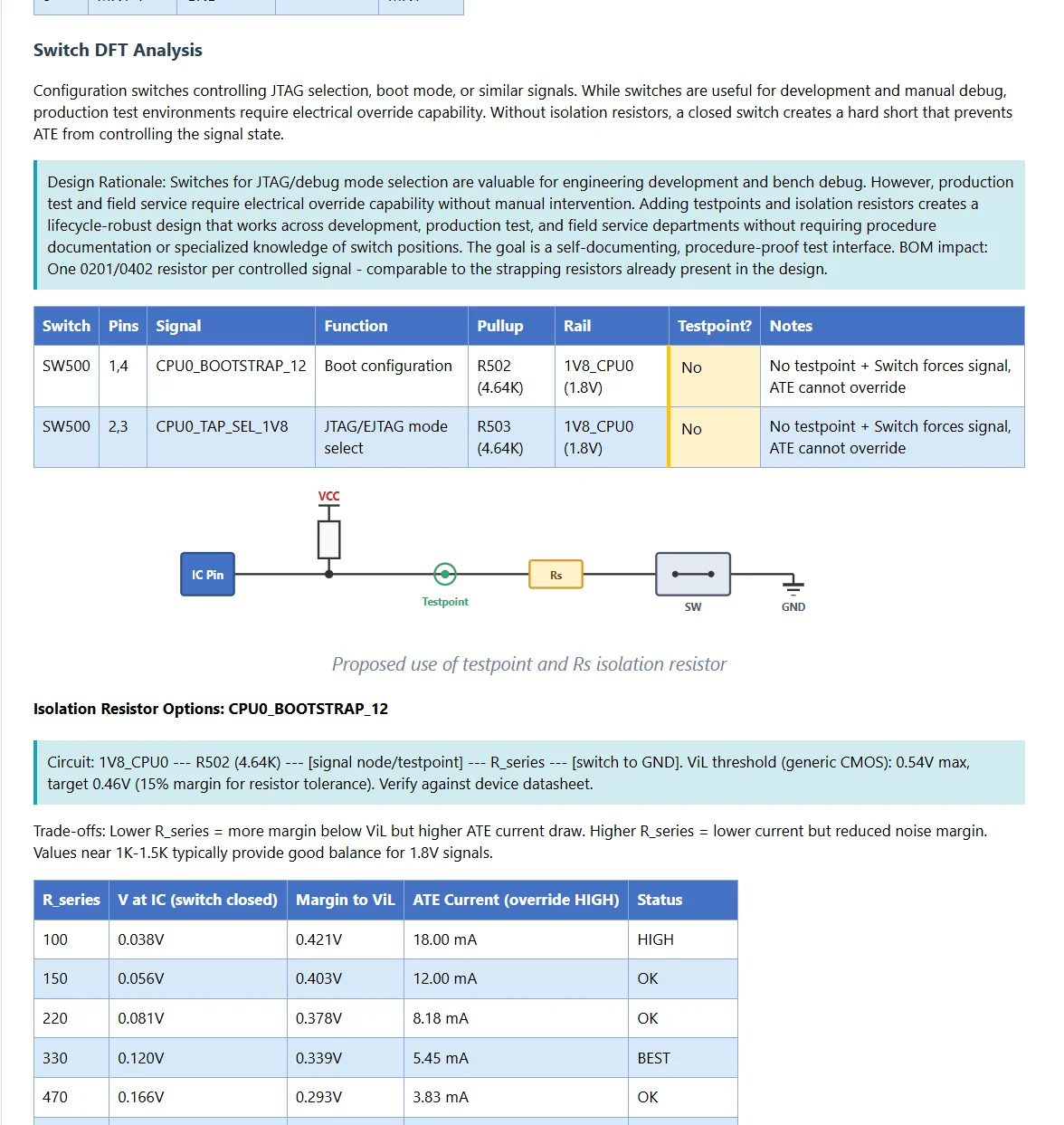

ניתוח DFT של מתגים — מזהה מתגי תצורה חסרי יכולת עקיפת בדיקה, מחשב ערכי נגד בידוד לתאימות ATE.

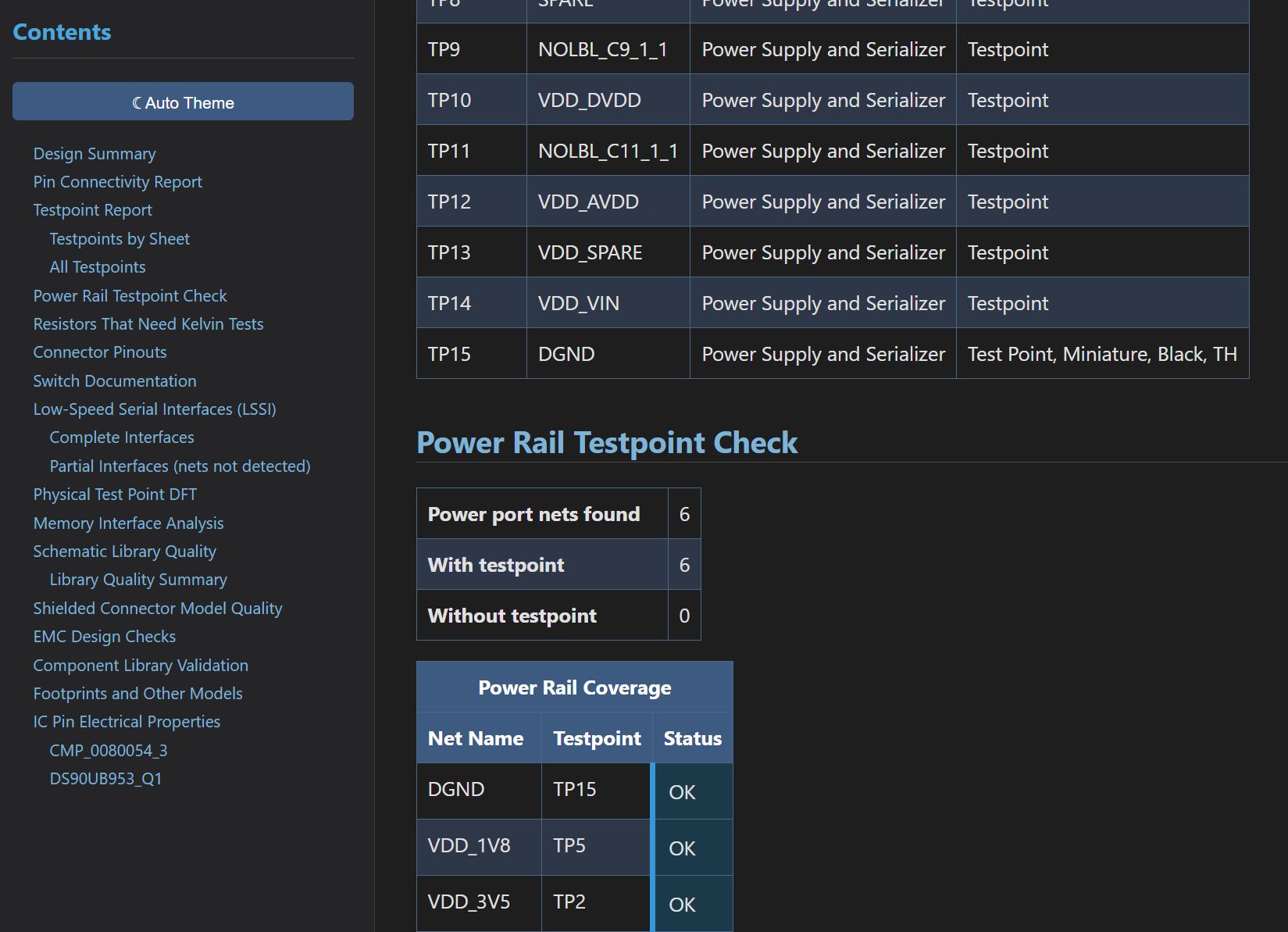

מלאי נקודות בדיקה עם ניתוח כיסוי מסילות מתח — כל רשת מתח נבדקת לגישת בדיקה.

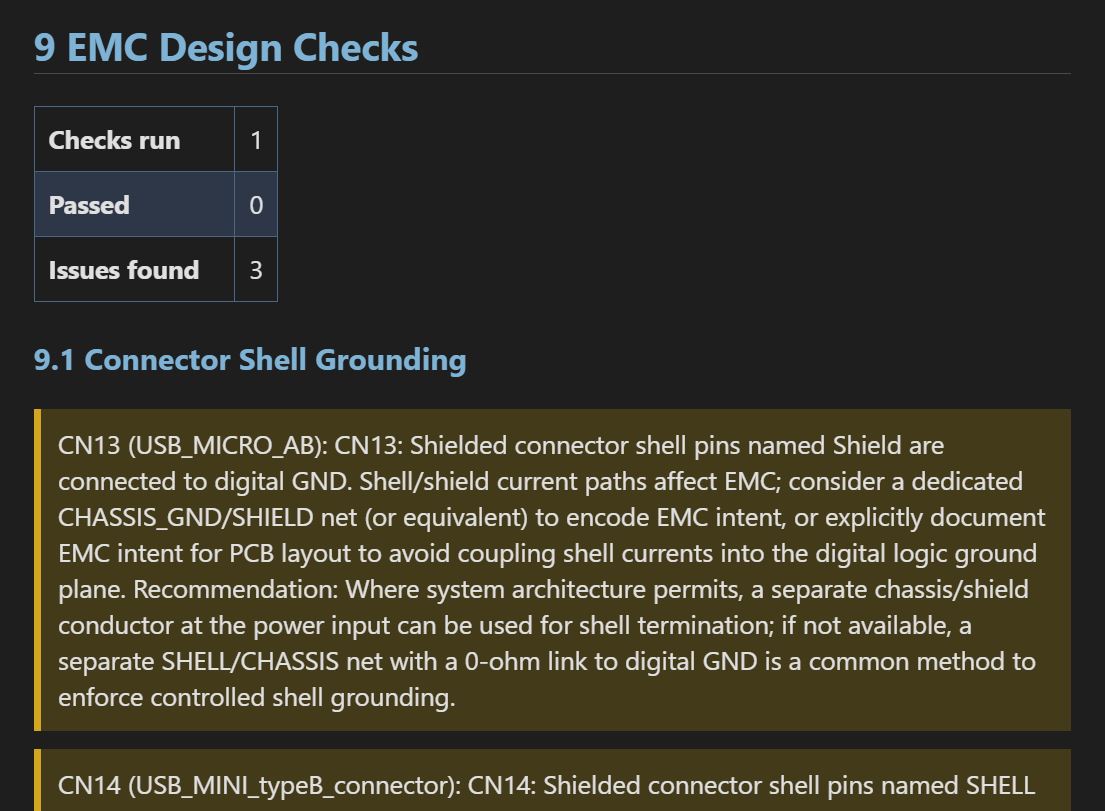

בדיקות עיצוב EMC, אימות ספריית רכיבים וביקורת טביעת רגל/מודל — הכל בדוח אחד.

לוח הניווט השמאלי מאפשר לכם לדלג ישירות לכל מקטע. הדוחות כוללים סיכום עיצוב, קישוריות פינים, ממשקי זיכרון, ממשקים טוריים, חיבורי מחברים, ניתוח DFT, דירוגי איכות ספריות ועוד.

מיקוד נוכחי: עיצובים דיגיטליים ומעורבים — מעבדים, FPGA, ממשקי זיכרון, אפיקים טוריים וניתוח יכולת בדיקה. בדיקות ספציפיות לאנלוגי (יציבות לולאת ספק כוח, ניתוח מסננים) נמצאות במפת הדרכים.

מה להעלות

דחסו את קבצי הסכמטיקה שלכם ל-ZIP והעלו. הנה מה שאנחנו צריכים:

קבצי סכמטיקה (נדרש)

קבצי Altium .SchDoc או KiCad .kicad_sch — כללו את כל הדפים המצוינים בהיררכיה.

קבצי פרויקט (מומלץ)

Altium: .PrjPcb, .PrjPcbStructure, .PrjPcbVariants. KiCad: .kicad_pro. אלה מספרים לנו את ההיררכיה ואת הדף העליון. בלעדיהם, תצטרכו לציין את שם הדף העליון, או שנניח עיצוב שטוח.

קבצי *.bsdl (רשות)

קבצי Boundary Scan Description Language. קבצים אלה משתמשים ב-IEEE 1149.1-2013 לתיאור יכולת הבדיקה של מעגלים משולבים דיגיטליים. אם מסופקים, Tomachie ינתח את הנכונות, התאימות ו-Design-for-Test של העיצוב שלכם.

טיפ: כשמבקשים סכמטיקות ממעצב או קבלן, בקשו את קבצי הפרויקט (.PrjPcb או .kicad_pro) יחד עם קבצי הסכמטיקה. מעצבים רבים שוכחים לכלול אותם.