설계 검토 문서 예시

Standard ERC looks at nets. Tomachie looks at paths — verifying differential pair integrity and impedance continuity across the entire signal chain, even through passive components and connectors. It finds what's hidden: mischaracterized pins, broken impedance paths, and invisible property errors that break your layout wizards. These pre-generated reports show the full analysis output, each containing 10,000+ words of DFT analysis, EMC checks, PCOLA-SOQ scoring, connector pinouts, and testpoint coverage documentation:

- FPGA1394V3 설계 검토 — Xilinx XC7Z020 FPGA가 포함된 IEEE 1394 FireWire 인터페이스, BSDL 바운더리 스캔 분석, JTAG 체인 검증

- MB1191 설계 검토 — ARM Cortex-M 프로세서가 포함된 STM32 Nucleo-144 개발 보드

- TIDA-050036 설계 검토 — Texas Instruments 산업용 베이스 보드 레퍼런스 설계

체험용 샘플

- FPGA1394V3.zip — Xilinx FPGA가 포함된 IEEE 1394 FireWire 인터페이스, 다중 시트 계층 구조

- MB1191.zip — STM32 Nucleo-144 개발 보드 (ST Microelectronics)

- TIDA-050036.zip — Texas Instruments 산업용 베이스 보드 레퍼런스 설계

샘플을 다운로드하여 제출 페이지에서 업로드하면 전체 분석 보고서를 받을 수 있습니다.

샘플 보고서 출력

Tomachie는 탐색 가능한 섹션이 포함된 대화형 HTML 보고서를 생성합니다. 다음과 같은 내용을 받게 됩니다:

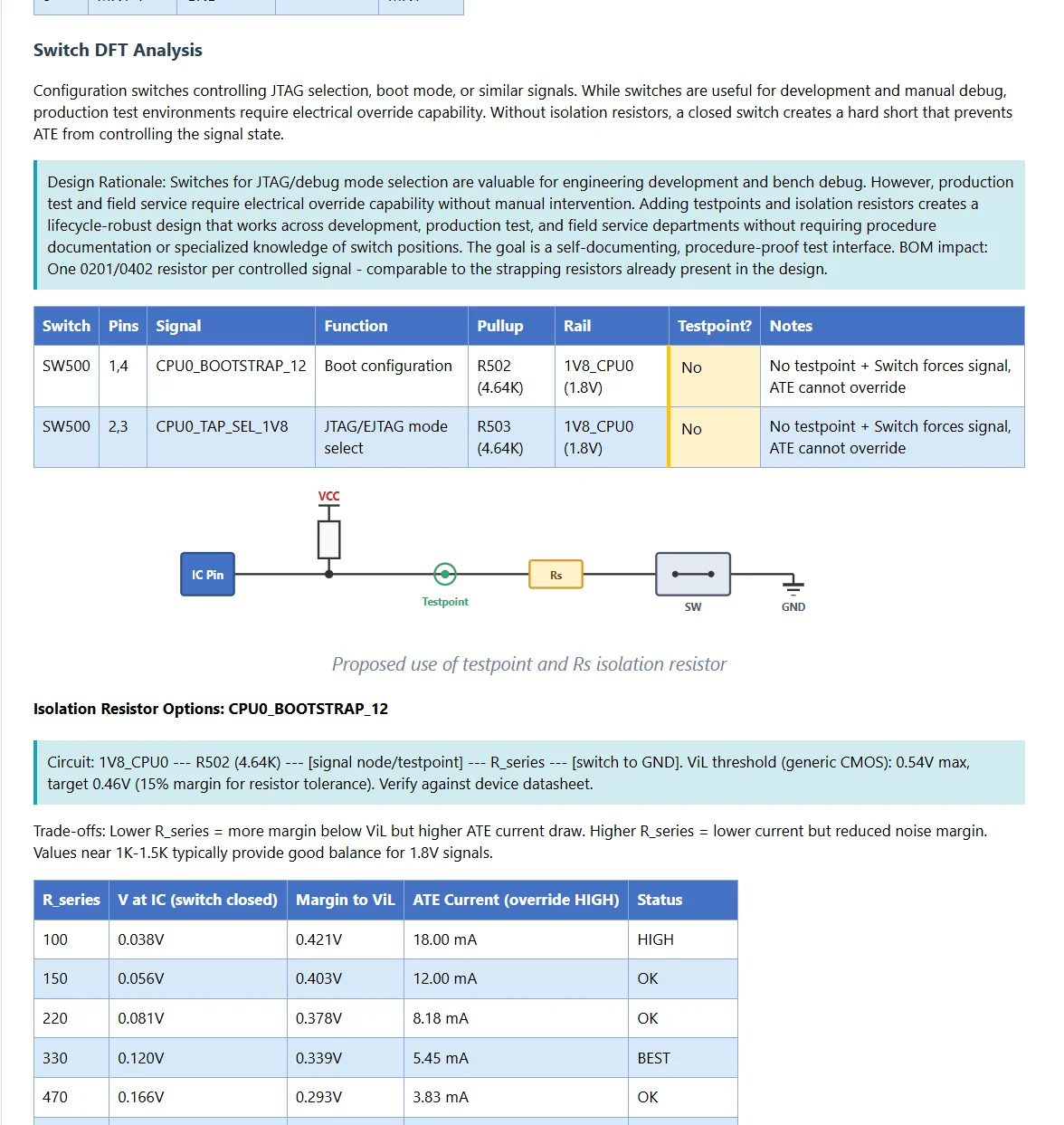

스위치 DFT 분석 — 테스트 오버라이드 기능이 부족한 구성 스위치를 식별하고, ATE 호환성을 위한 절연 저항 값을 계산합니다.

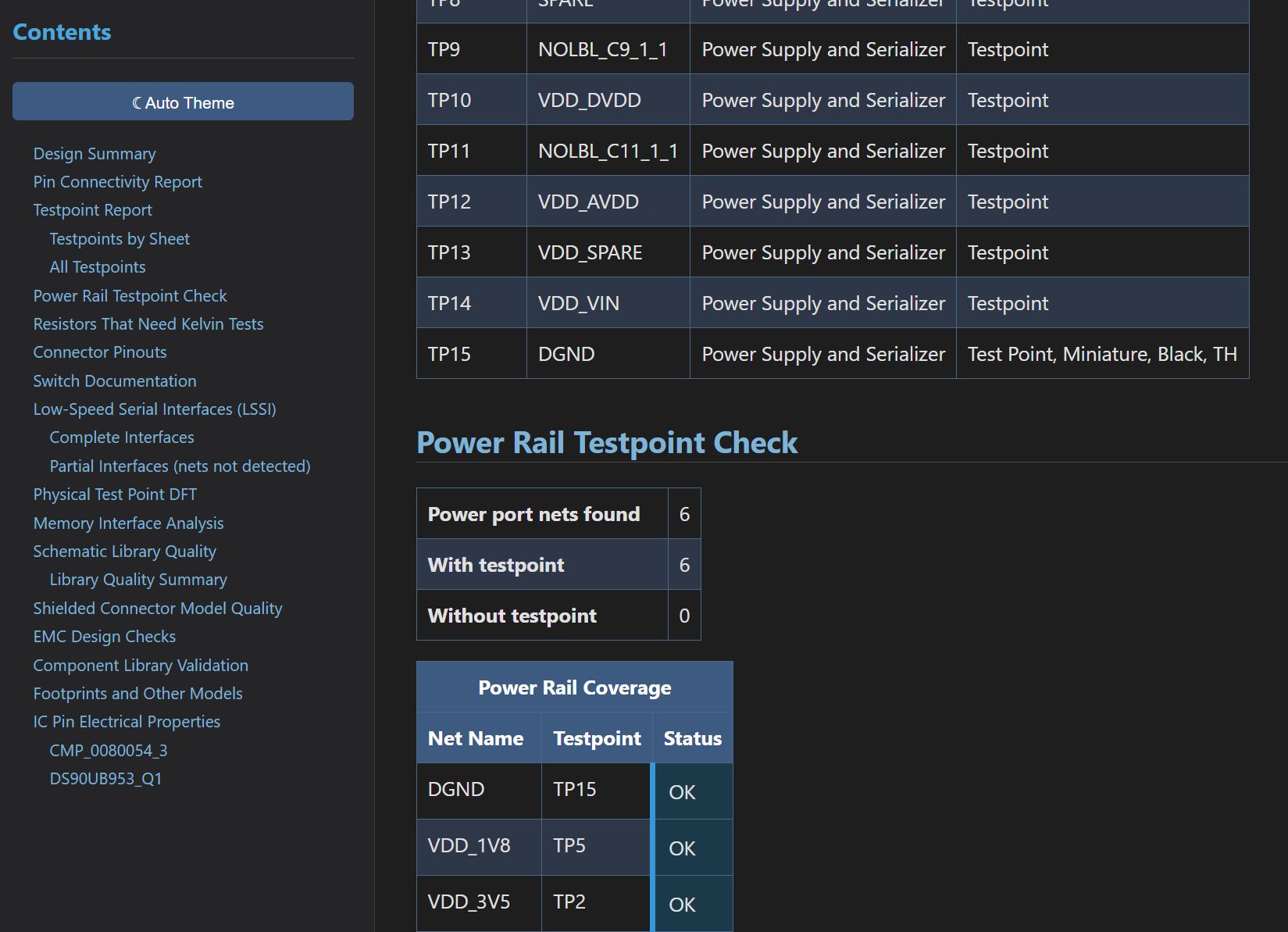

전원 레일 커버리지 분석이 포함된 테스트포인트 인벤토리 — 모든 전원 넷의 테스트 액세스를 확인합니다.

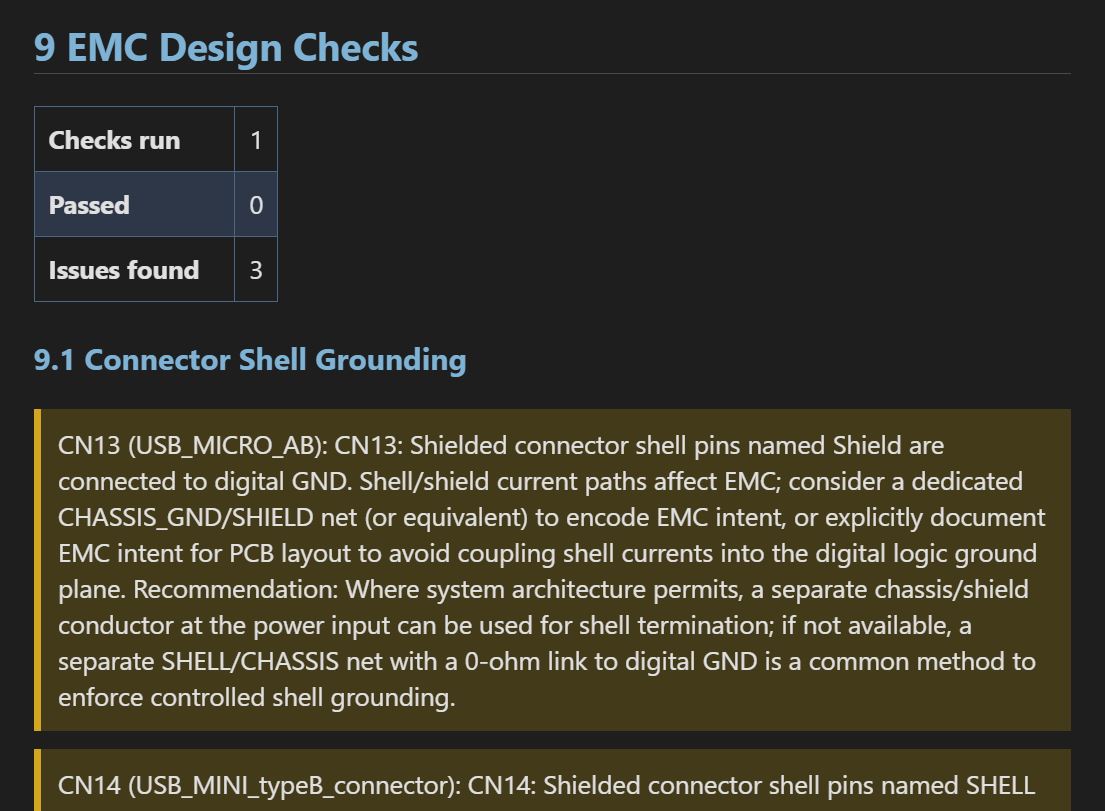

EMC 설계 검사, 부품 라이브러리 검증, 풋프린트/모델 감사 — 모두 하나의 보고서에.

좌측 탐색 패널에서 원하는 섹션으로 바로 이동할 수 있습니다. 보고서에는 설계 요약, 핀 연결, 메모리 인터페이스, 직렬 인터페이스, 커넥터 핀아웃, DFT 분석, 라이브러리 품질 등급 등이 포함됩니다.

현재 초점: 디지털 및 혼합 신호 설계 — 프로세서, FPGA, 메모리 인터페이스, 직렬 버스 및 테스트 가능성 분석. 아날로그 전용 검사 (전원 공급 루프 안정성, 필터 분석)는 로드맵에 포함되어 있습니다.

업로드 대상

회로도 파일을 ZIP으로 압축하여 업로드하세요. 필요한 항목:

회로도 파일 (필수)

Altium .SchDoc 또는 KiCad .kicad_sch 파일 — 계층 구조에서 참조하는 모든 시트를 포함하세요.

프로젝트 파일 (권장)

Altium: .PrjPcb, .PrjPcbStructure, .PrjPcbVariants. KiCad: .kicad_pro. 계층 구조와 최상위 시트를 알려줍니다. 이 파일이 없으면 최상위 시트 이름을 지정해야 하며, 지정하지 않으면 플랫 설계로 간주합니다.

*.bsdl 파일 (선택사항)

바운더리 스캔 기술 언어 파일. IEEE 1149.1-2013을 사용하여 디지털 IC의 테스트 기능을 설명합니다. 제공하면 Tomachie가 설계의 정확성, 규정 준수 및 DFT를 분석합니다.

팁: 설계자나 계약업체에 회로도를 요청할 때 회로도 파일과 함께 프로젝트 파일 (.PrjPcb 또는 .kicad_pro)도 요청하세요. 많은 설계자들이 이를 포함하는 것을 잊어버립니다.