Örnek Tasarım İnceleme Belgeleri

Standard ERC looks at nets. Tomachie looks at paths — verifying differential pair integrity and impedance continuity across the entire signal chain, even through passive components and connectors. It finds what's hidden: mischaracterized pins, broken impedance paths, and invisible property errors that break your layout wizards. These pre-generated reports show the full analysis output, each containing 10,000+ words of DFT analysis, EMC checks, PCOLA-SOQ scoring, connector pinouts, and testpoint coverage documentation:

- FPGA1394V3 Tasarım İncelemesi — Xilinx XC7Z020 FPGA ile IEEE 1394 FireWire arayüzü, BSDL sınır tarama analizi, JTAG zincir doğrulaması

- MB1191 Tasarım İncelemesi — ARM Cortex-M işlemcili STM32 Nucleo-144 geliştirme kartı

- TIDA-050036 Tasarım İncelemesi — Texas Instruments endüstriyel temel kart referans tasarımı

Deneyebileceğiniz Örnekler

- FPGA1394V3.zip — Xilinx FPGA ile IEEE 1394 FireWire arayüzü, çoklu sayfa hiyerarşisi

- MB1191.zip — STM32 Nucleo-144 geliştirme kartı (ST Microelectronics)

- TIDA-050036.zip — Texas Instruments endüstriyel temel kart referans tasarımı

Herhangi bir örneği indirin, Gönder sayfasında yükleyin ve tam bir analiz raporu alın.

Örnek Rapor Çıktısı

Tomachie, gezinilebilir bölümler içeren etkileşimli bir HTML raporu oluşturur. İşte alacaklarınız:

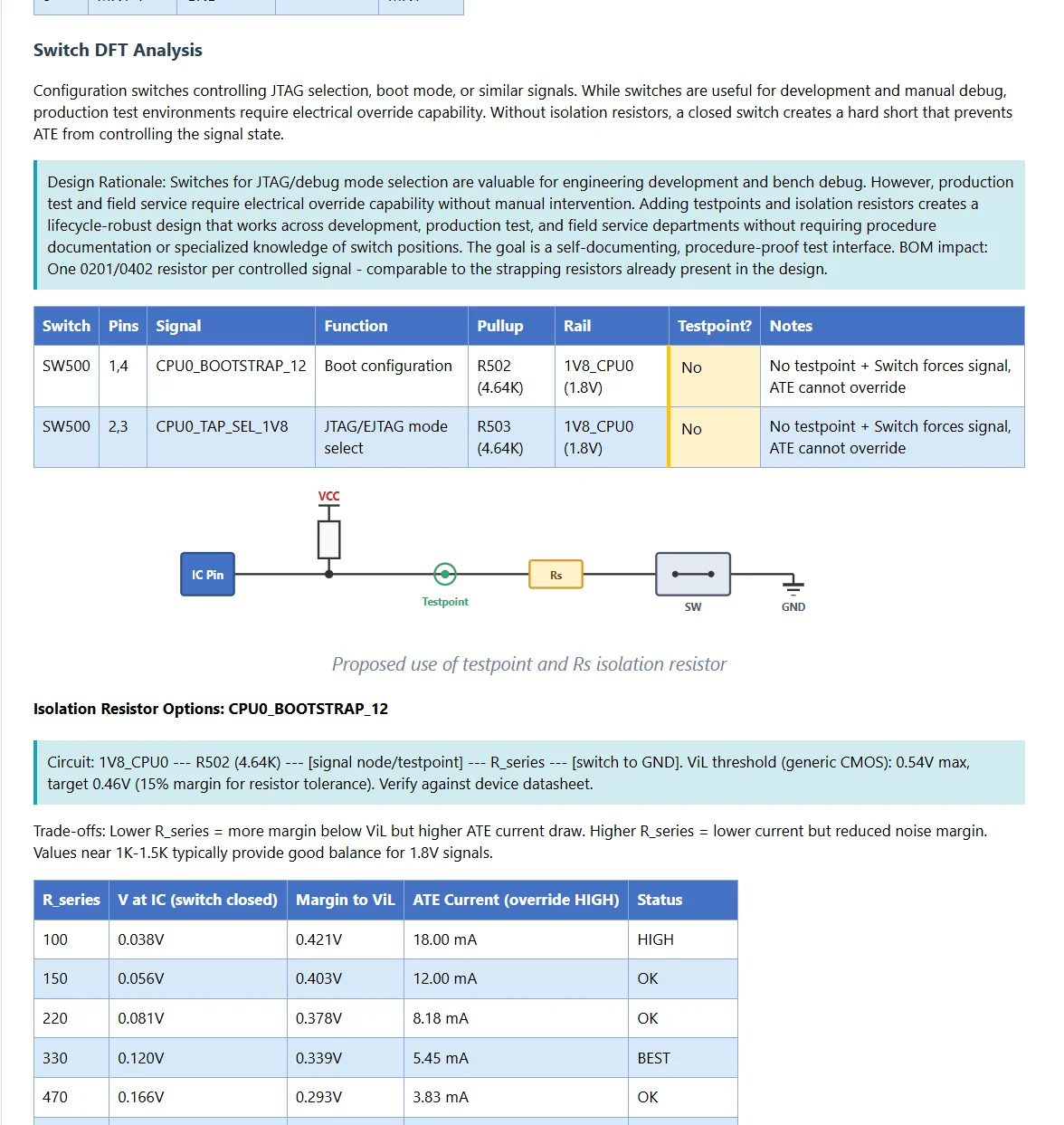

Anahtar DFT analizi — test geçersiz kılma özelliği eksik olan yapılandırma anahtarlarını tanımlar, ATE uyumluluğu için izolasyon direnç değerlerini hesaplar.

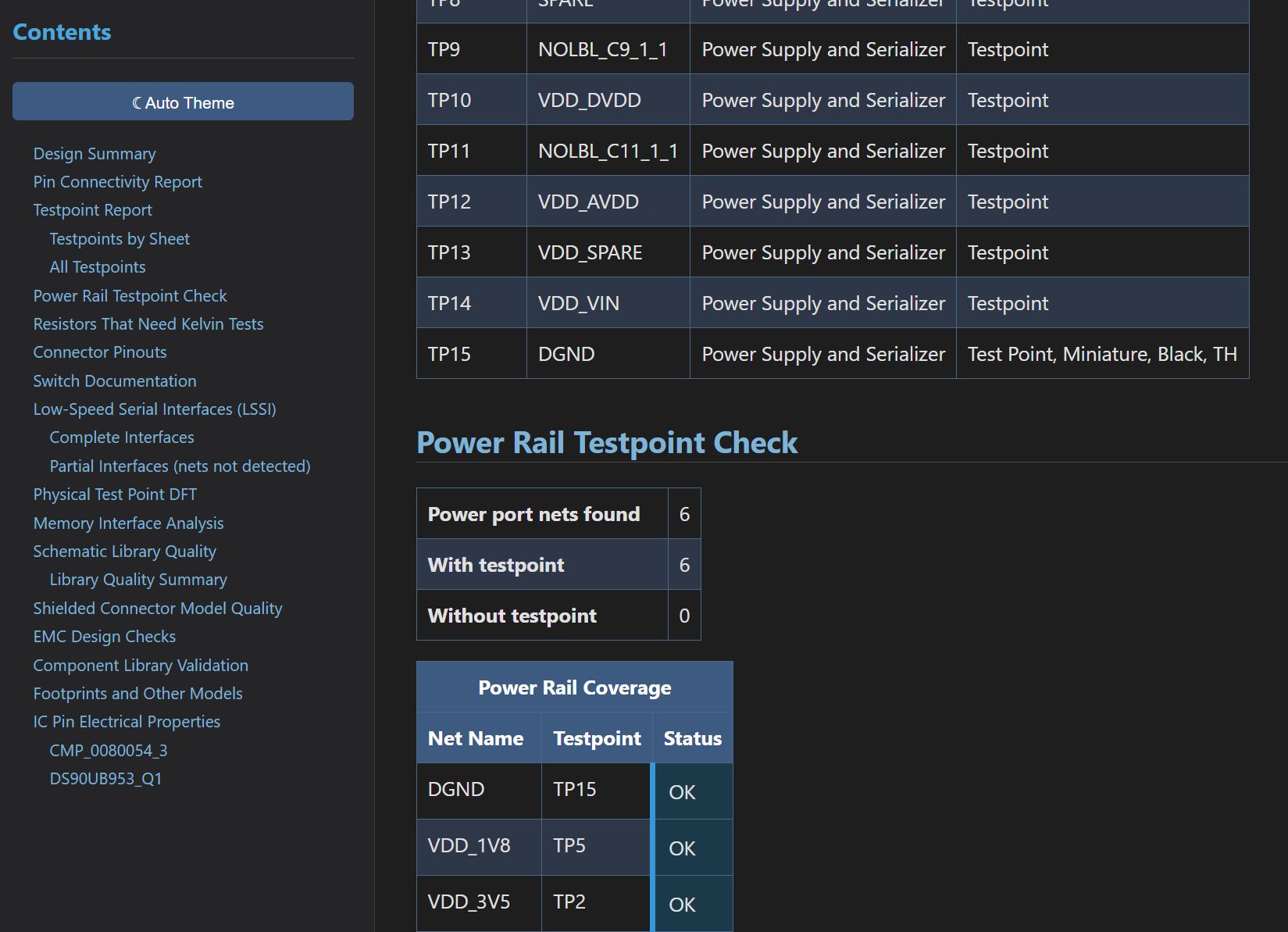

Güç hattı kapsam analizi ile test noktası envanteri — her güç neti test erişimi için kontrol edilir.

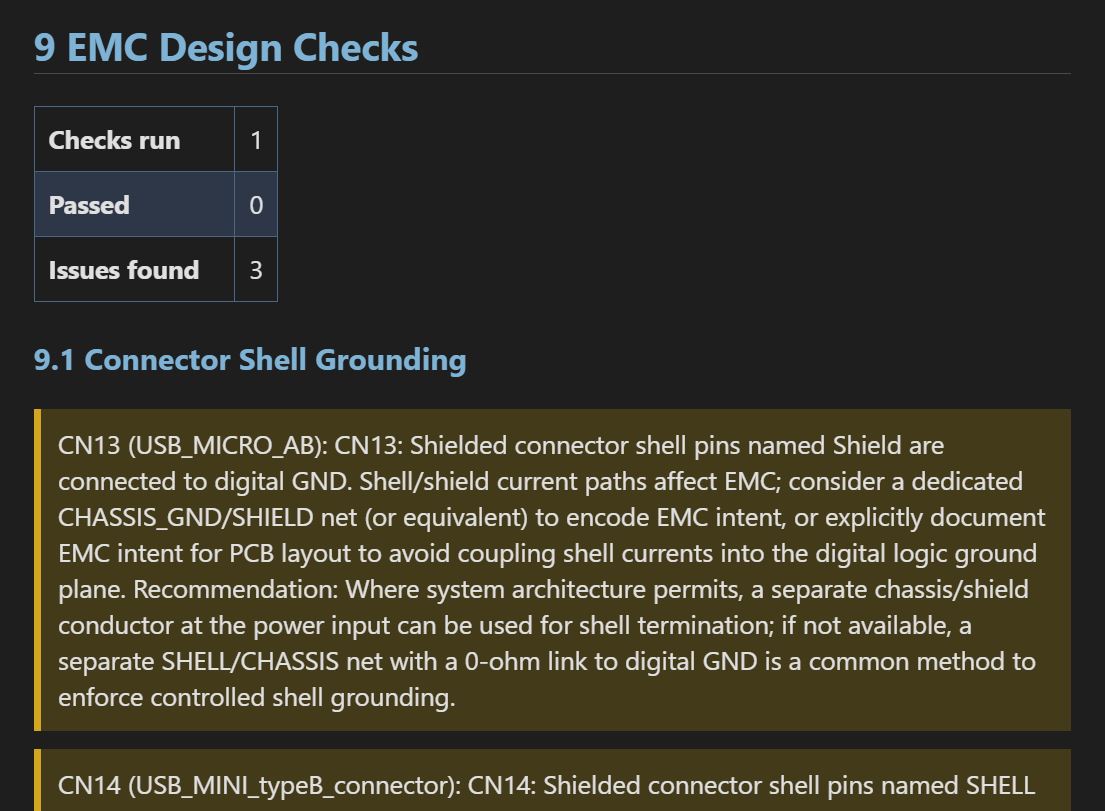

EMC tasarım kontrolleri, bileşen kütüphane doğrulaması ve ayak izi/model denetimi — hepsi tek bir raporda.

Sol gezinme paneli herhangi bir bölüme doğrudan atlamanızı sağlar. Raporlar Tasarım Özeti, Pin Bağlantısı, Bellek Arayüzleri, Seri Arayüzler, Konnektör Pinoutları, DFT Analizi, Kütüphane Kalite dereceleri ve daha fazlasını içerir.

Mevcut Odak: Dijital ve karma sinyal tasarımları — işlemciler, FPGA'lar, bellek arayüzleri, seri veriyolları ve test edilebilirlik analizi. Analog'a özel kontroller (güç kaynağı döngü kararlılığı, filtre analizi) yol haritasındadır.

Ne Yüklenmeli

Şematik dosyalarınızı ZIP yapın ve yükleyin. İhtiyacımız olanlar:

Şematik dosyalar (gerekli)

Altium .SchDoc veya KiCad .kicad_sch dosyaları — hiyerarşi tarafından referans verilen tüm sayfaları dahil edin.

Proje dosyaları (önerilen)

Altium: .PrjPcb, .PrjPcbStructure, .PrjPcbVariants. KiCad: .kicad_pro. Bunlar bize hiyerarşiyi ve üst düzey sayfayı söyler. Bunlar olmadan üst sayfa adını belirtmeniz gerekir, aksi takdirde düz bir tasarım varsayacağız.

*.bsdl dosyaları (isteğe bağlı)

Sınır Tarama Açıklama Dili dosyaları. Bu dosyalar dijital IC'lerin test yeteneğini tanımlamak için IEEE 1149.1-2013 kullanır. Sağlandığında, Tomachie tasarımınızın doğruluğunu, uyumluluğunu ve Test için Tasarımını analiz edecektir.

İpucu: Bir tasarımcı veya yükleniciden şematik talep ederken, şematik dosyalarla birlikte proje dosyalarını (.PrjPcb veya .kicad_pro) isteyin. Birçok tasarımcı bunları dahil etmeyi unutur.