設計審查文件範例

Standard ERC looks at nets. Tomachie looks at paths — verifying differential pair integrity and impedance continuity across the entire signal chain, even through passive components and connectors. It finds what's hidden: mischaracterized pins, broken impedance paths, and invisible property errors that break your layout wizards. These pre-generated reports show the full analysis output, each containing 10,000+ words of DFT analysis, EMC checks, PCOLA-SOQ scoring, connector pinouts, and testpoint coverage documentation:

- FPGA1394V3 設計審查 — IEEE 1394 FireWire 介面搭配 Xilinx XC7Z020 FPGA、BSDL 邊界掃描分析、JTAG 鏈驗證

- MB1191 設計審查 — 搭載 ARM Cortex-M 處理器的 STM32 Nucleo-144 開發板

- TIDA-050036 設計審查 — Texas Instruments 工業基板參考設計

您可以嘗試的範例

- FPGA1394V3.zip — IEEE 1394 FireWire 介面搭配 Xilinx FPGA,多層架構

- MB1191.zip — STM32 Nucleo-144 開發板 (ST Microelectronics)

- TIDA-050036.zip — Texas Instruments 工業基板參考設計

下載任何範例,在提交頁面上傳,即可獲得完整的分析報告。

範例報告輸出

Tomachie 產生互動式 HTML 報告,含可導覽的章節。以下是您將收到的內容:

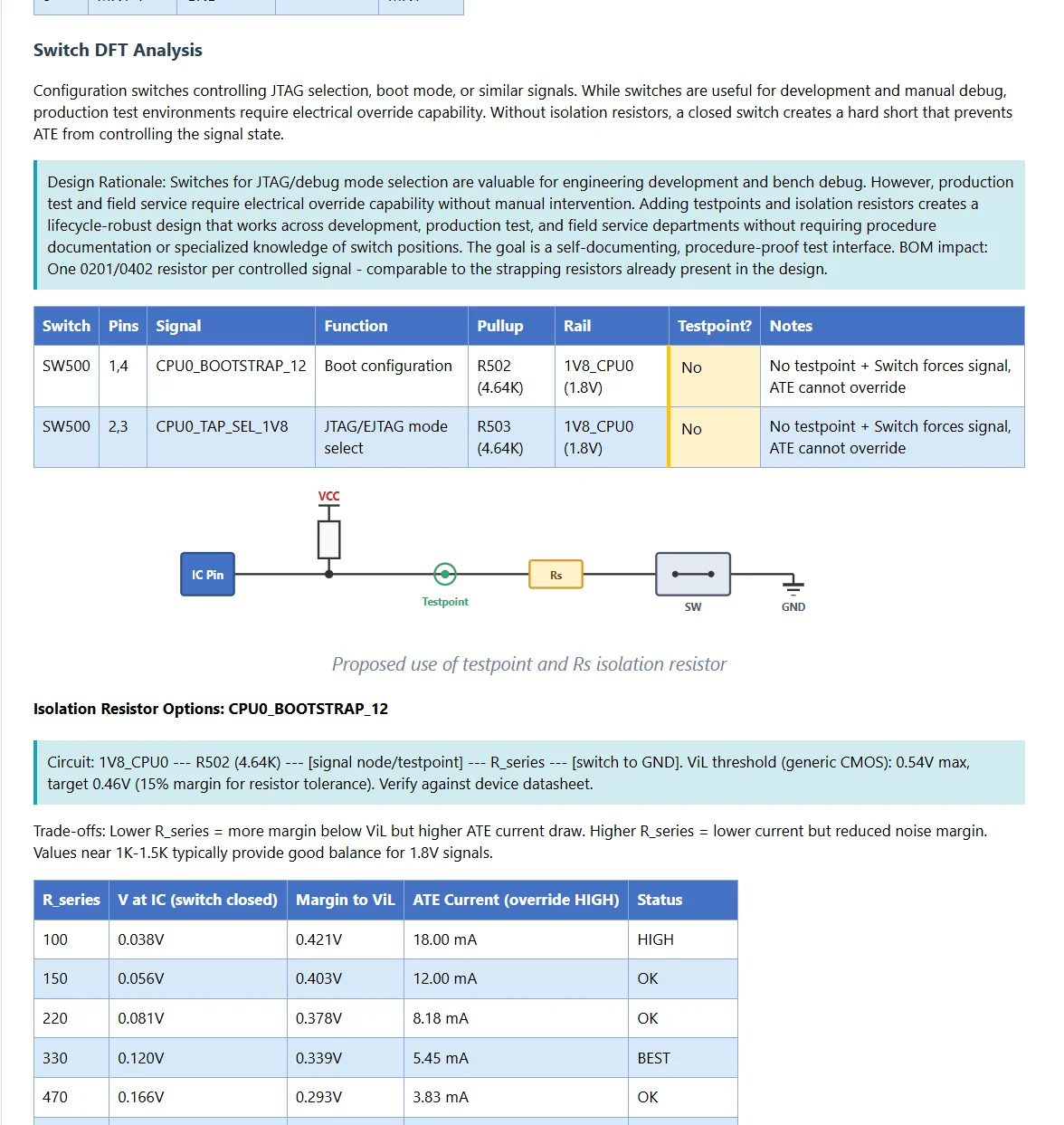

開關 DFT 分析 — 識別缺少測試覆寫能力的配置開關,計算 ATE 相容性的隔離電阻值。

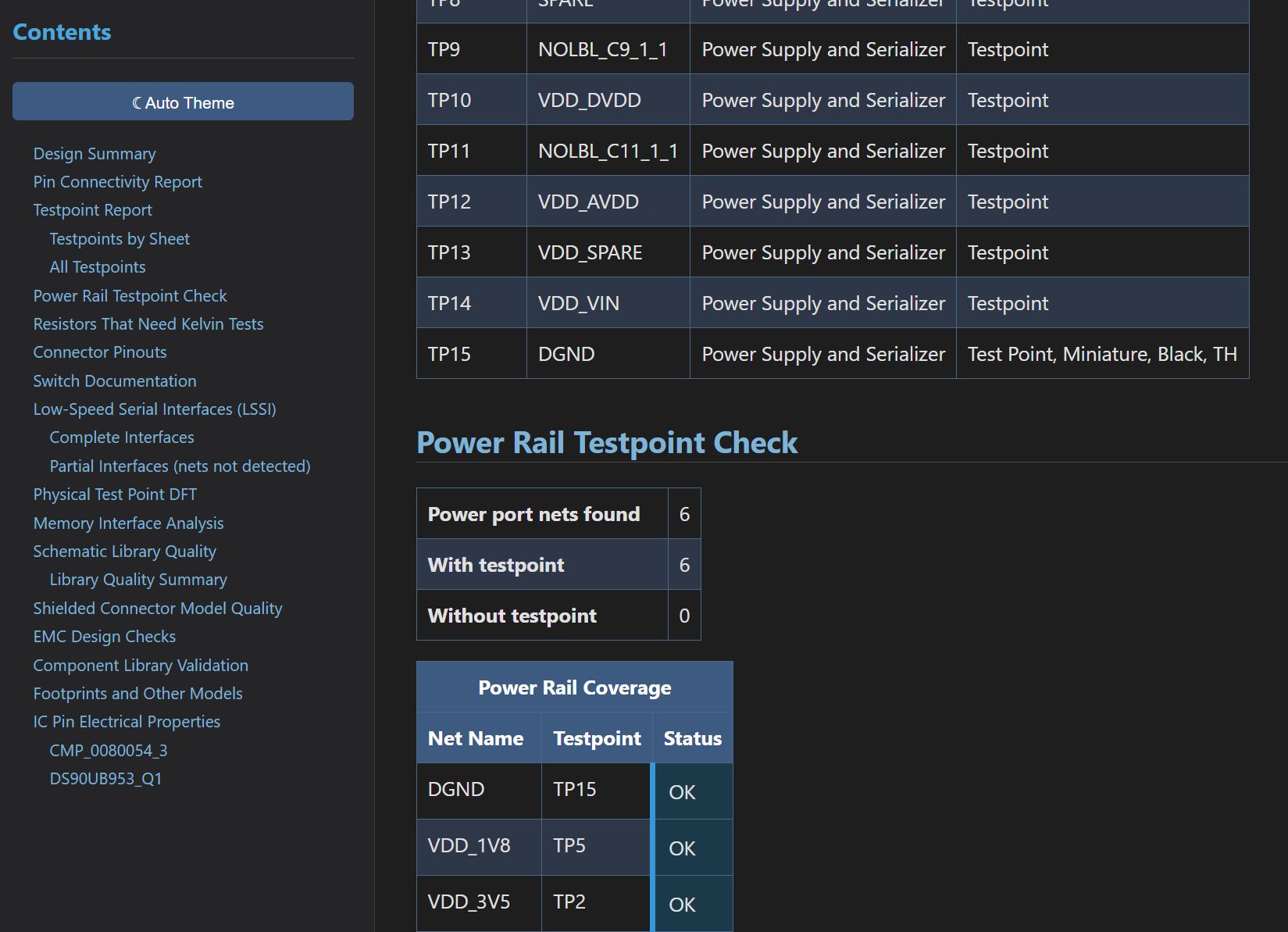

測試點清單及電源軌覆蓋分析 — 每個電源網路均檢查測試存取。

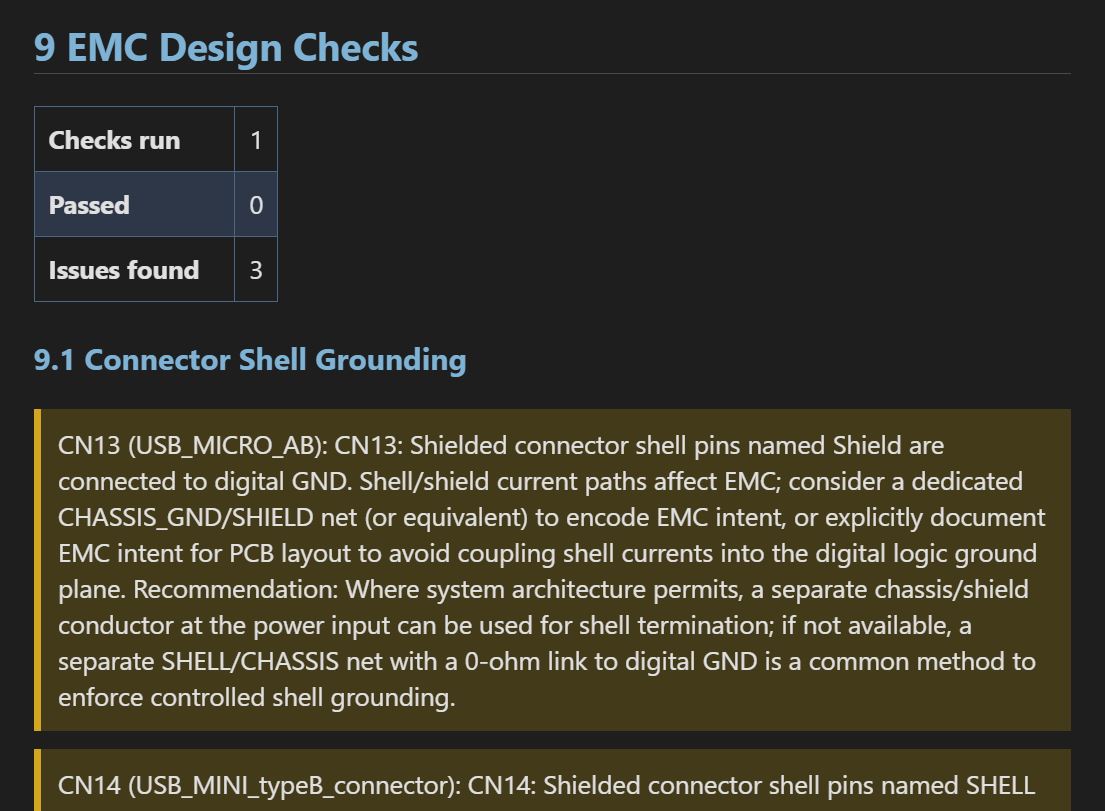

EMC 設計檢查、元件庫驗證和 footprint/模型稽核 — 全部在一份報告中。

左側導覽面板可讓您直接跳至任何章節。報告包括設計摘要、腳位連接、記憶體介面、串列介面、連接器腳位、DFT 分析、元件庫品質評分等。

目前重點: 數位及混合信號設計 — 處理器、FPGA、記憶體介面、串列匯流排及可測試性分析。類比專用檢查(電源供應迴路穩定性、濾波器分析)已列入發展藍圖。

上傳內容

將您的電路圖檔案壓縮為 ZIP 後上傳。以下是我們需要的內容:

電路圖檔案 (必要)

Altium .SchDoc 或 KiCad .kicad_sch 檔案 — 包含階層引用的所有圖紙。

專案檔案 (建議)

Altium:.PrjPcb、.PrjPcbStructure、.PrjPcbVariants。KiCad:.kicad_pro。這些檔案告訴我們階層和頂層圖紙。若未提供,您需要指定頂層圖紙名稱,否則我們將假設為平面設計。

*.bsdl 檔案 (選填)

邊界掃描描述語言檔案。這些檔案使用 IEEE 1149.1-2013 描述數位 IC 的測試能力。若提供,Tomachie 將分析您設計的正確性、合規性和可測試性設計。

提示: 向設計師或承包商索取電路圖時,請要求同時提供專案檔案(.PrjPcb 或 .kicad_pro)。許多設計師會忘記附上。