Beispiel-Designprüfungsdokumente

Standard ERC looks at nets. Tomachie looks at paths — verifying differential pair integrity and impedance continuity across the entire signal chain, even through passive components and connectors. It finds what's hidden: mischaracterized pins, broken impedance paths, and invisible property errors that break your layout wizards. These pre-generated reports show the full analysis output, each containing 10,000+ words of DFT analysis, EMC checks, PCOLA-SOQ scoring, connector pinouts, and testpoint coverage documentation:

- FPGA1394V3-Designprüfung — IEEE 1394 FireWire-Schnittstelle mit Xilinx XC7Z020 FPGA, BSDL-Boundary-Scan-Analyse, JTAG-Kettenvalidierung

- MB1191-Designprüfung — STM32 Nucleo-144 Entwicklungsboard mit ARM Cortex-M Prozessor

- TIDA-050036-Designprüfung — Texas Instruments industrielles Baseboard-Referenzdesign

Beispiele zum Ausprobieren

- FPGA1394V3.zip — IEEE 1394 FireWire-Schnittstelle mit Xilinx FPGA, mehrseitige Hierarchie

- MB1191.zip — STM32 Nucleo-144 Entwicklungsboard (ST Microelectronics)

- TIDA-050036.zip — Texas Instruments industrielles Baseboard-Referenzdesign

Laden Sie ein Beispiel herunter, laden Sie es auf der Einreichen-Seite hoch und erhalten Sie einen vollständigen Analysebericht.

Beispiel-Berichtsausgabe

Tomachie generiert einen interaktiven HTML-Bericht mit navigierbaren Abschnitten. Folgendes erhalten Sie:

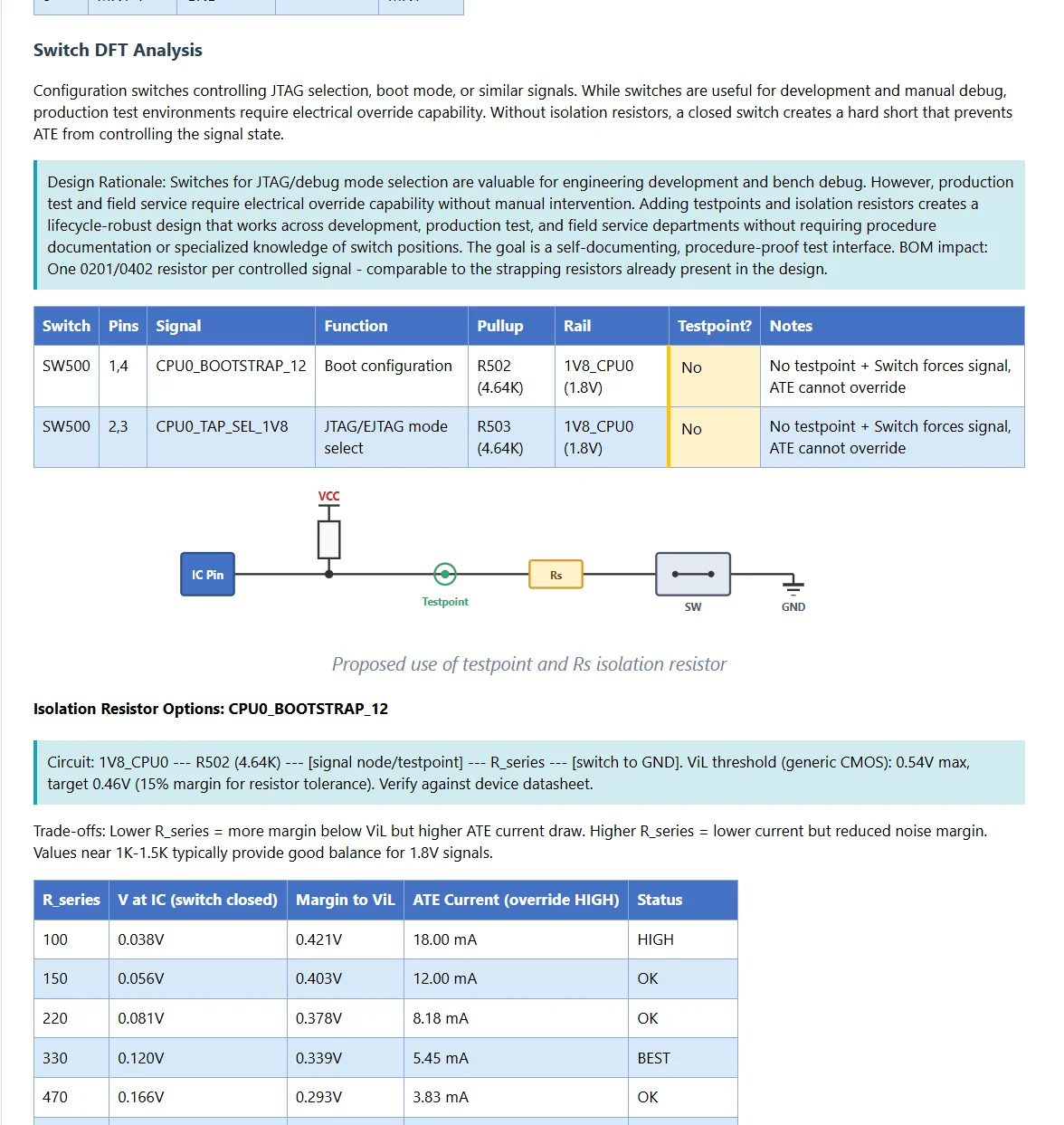

Switch-DFT-Analyse — identifiziert Konfigurationsschalter ohne Test-Override-Fähigkeit, berechnet Isolationswiderstandswerte für ATE-Kompatibilität.

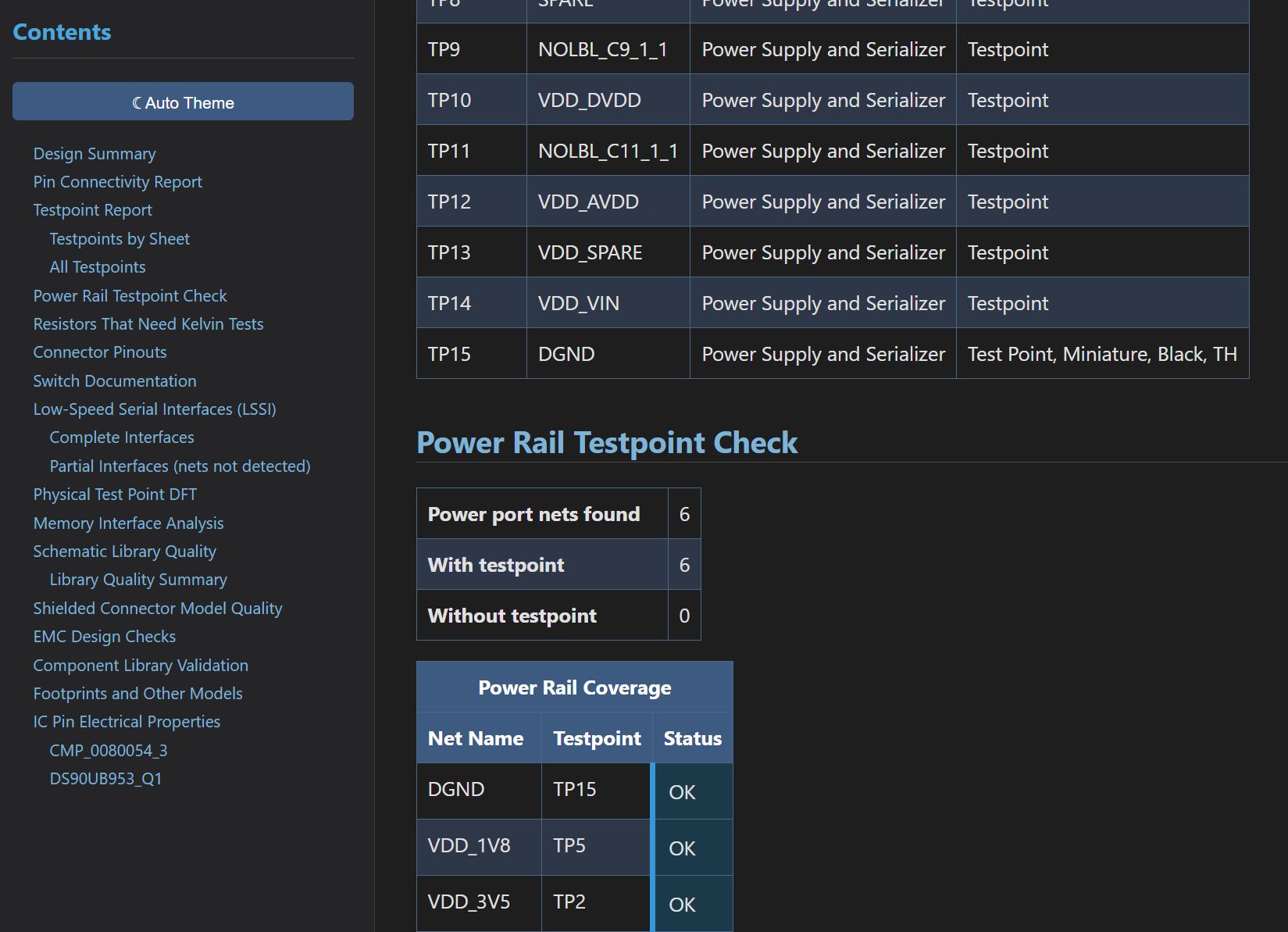

Testpunkt-Inventar mit Versorgungsnetzabdeckungsanalyse — jedes Versorgungsnetz auf Testzugang geprüft.

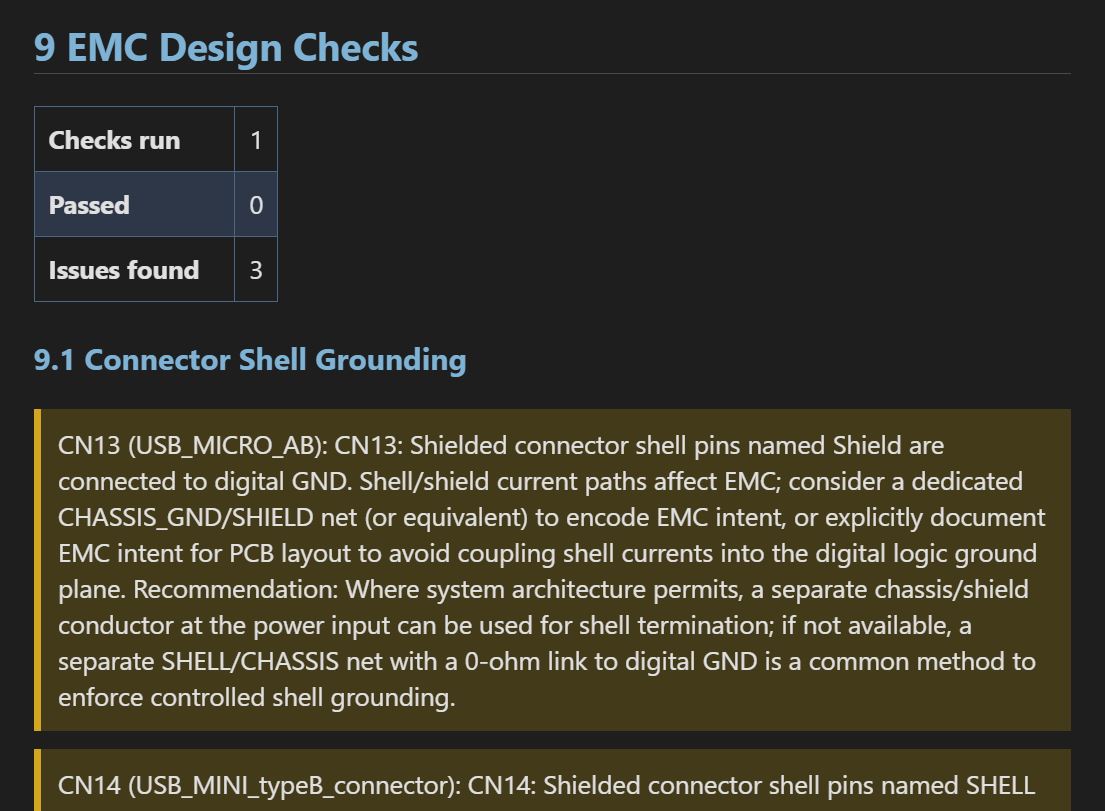

EMV-Designprüfungen, Bauteilbibliotheksvalidierung und Footprint-/Modell-Audit — alles in einem Bericht.

Das linke Navigationspanel ermöglicht den direkten Sprung zu jedem Abschnitt. Berichte umfassen Design-Zusammenfassung, Pin-Konnektivität, Speicherschnittstellen, serielle Schnittstellen, Stecker-Pinouts, DFT-Analyse, Bibliotheksqualitätsbewertungen und mehr.

Aktueller Fokus: Digitale und Mixed-Signal-Designs — Prozessoren, FPGAs, Speicherschnittstellen, serielle Busse und Testbarkeitsanalyse. Analogspezifische Prüfungen (Netzteil-Regelkreisstabilität, Filteranalyse) sind auf der Roadmap.

Was hochzuladen ist

Packen Sie Ihre Schaltplandateien als ZIP und laden Sie hoch. Folgendes benötigen wir:

Schaltplandateien (erforderlich)

Altium .SchDoc oder KiCad .kicad_sch Dateien — schließen Sie alle Blätter ein, die von der Hierarchie referenziert werden.

Projektdateien (empfohlen)

Altium: .PrjPcb, .PrjPcbStructure, .PrjPcbVariants. KiCad: .kicad_pro. Diese teilen uns die Hierarchie und das Top-Level-Blatt mit. Ohne sie müssen Sie den Top-Sheet-Namen angeben, oder wir nehmen ein flaches Design an.

*.bsdl Dateien (optional)

Boundary-Scan-Description-Language-Dateien. Diese Dateien verwenden IEEE 1149.1-2013, um die Testfähigkeit der digitalen ICs zu beschreiben. Falls bereitgestellt, analysiert Tomachie die Korrektheit, Konformität und Design-for-Test Ihres Designs.

Tipp: Wenn Sie Schaltpläne von einem Designer oder Auftragnehmer anfordern, bitten Sie um die Projektdateien (.PrjPcb oder .kicad_pro) zusammen mit den Schaltplandateien. Viele Designer vergessen, diese beizufügen.