Esempi di documenti di revisione design

Standard ERC looks at nets. Tomachie looks at paths — verifying differential pair integrity and impedance continuity across the entire signal chain, even through passive components and connectors. It finds what's hidden: mischaracterized pins, broken impedance paths, and invisible property errors that break your layout wizards. These pre-generated reports show the full analysis output, each containing 10,000+ words of DFT analysis, EMC checks, PCOLA-SOQ scoring, connector pinouts, and testpoint coverage documentation:

- Revisione design FPGA1394V3 — Interfaccia IEEE 1394 FireWire con FPGA Xilinx XC7Z020, analisi boundary scan BSDL, validazione catena JTAG

- Revisione design MB1191 — Scheda di sviluppo STM32 Nucleo-144 con processore ARM Cortex-M

- Revisione design TIDA-050036 — Design di riferimento scheda base industriale Texas Instruments

Campioni da provare

- FPGA1394V3.zip — Interfaccia IEEE 1394 FireWire con FPGA Xilinx, gerarchia multi-foglio

- MB1191.zip — Scheda di sviluppo STM32 Nucleo-144 (ST Microelectronics)

- TIDA-050036.zip — Design di riferimento scheda base industriale Texas Instruments

Scarica qualsiasi campione, caricalo nella pagina Invia e ricevi un report di analisi completo.

Esempio di output del report

Tomachie genera un report HTML interattivo con sezioni navigabili. Ecco cosa riceverai:

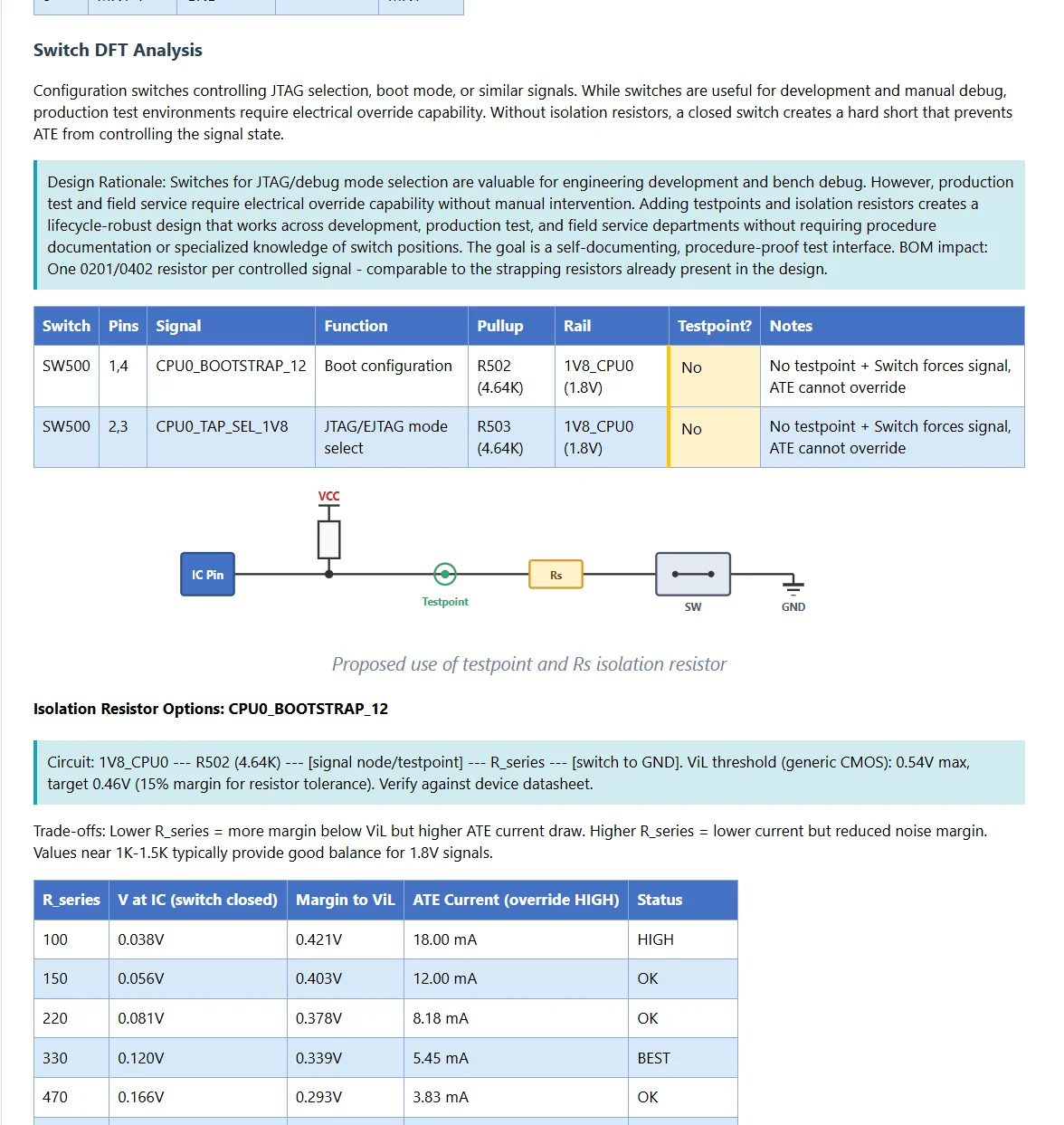

Analisi DFT degli switch — identifica gli switch di configurazione privi di capacità di override per il test, calcola i valori dei resistori di isolamento per la compatibilità ATE.

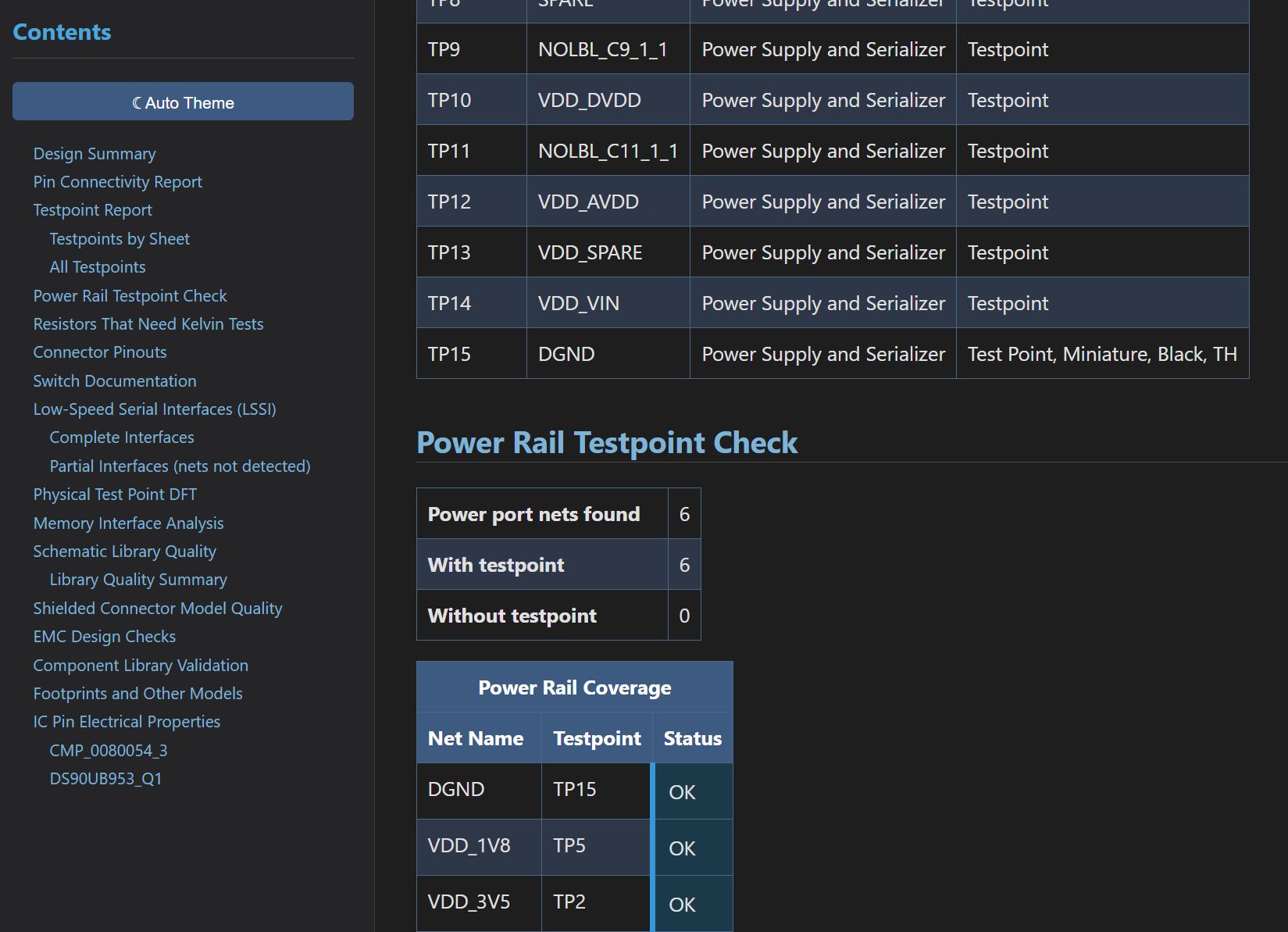

Inventario punti di test con analisi della copertura dei rail di alimentazione — ogni net di alimentazione verificata per l'accesso al test.

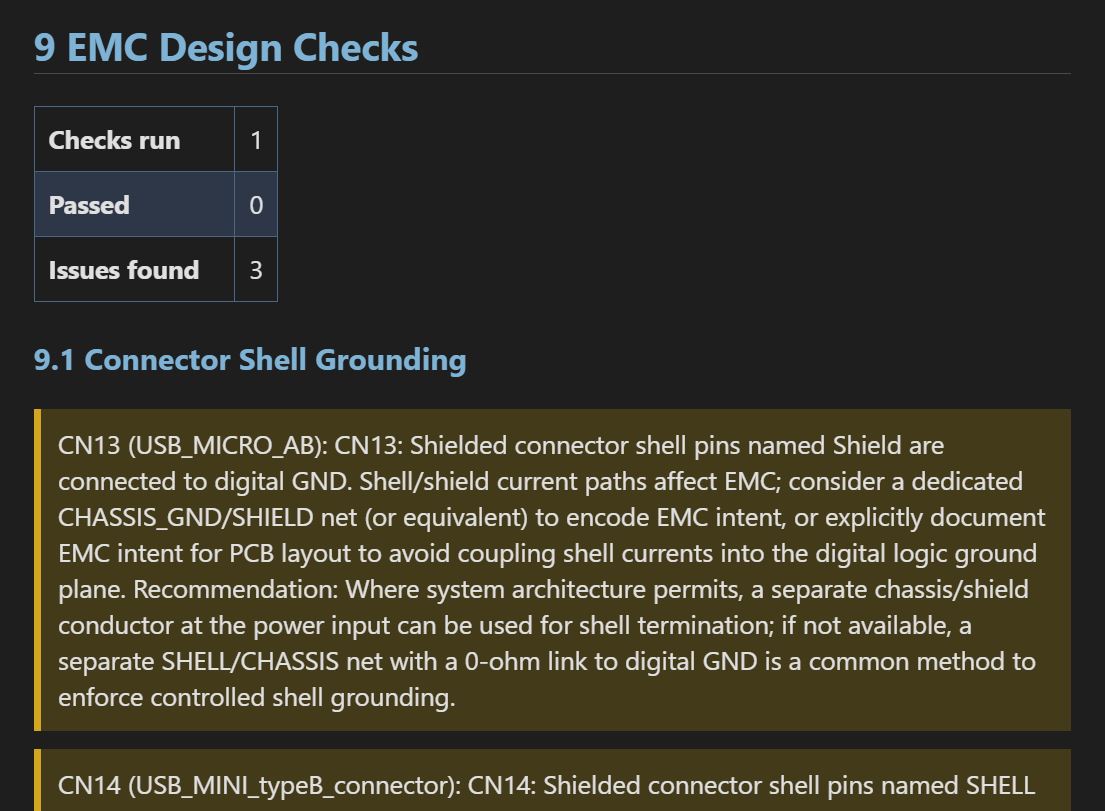

Controlli di design EMC, validazione delle librerie dei componenti e audit footprint/modello — tutto in un unico report.

Il pannello di navigazione a sinistra permette di saltare direttamente a qualsiasi sezione. I report includono Riepilogo design, Connettività pin, Interfacce di memoria, Interfacce seriali, Pinout connettori, Analisi DFT, Valutazioni qualità librerie e altro ancora.

Focus attuale: Design digitali e a segnale misto — processori, FPGA, interfacce di memoria, bus seriali e analisi di testabilità. I controlli specifici per l'analogico (stabilità del loop di alimentazione, analisi dei filtri) sono nella roadmap.

Cosa caricare

Comprimi i tuoi file schematici in ZIP e carica. Ecco cosa ci serve:

File schematici (obbligatorio)

File Altium .SchDoc o KiCad .kicad_sch — includi tutti i fogli referenziati dalla gerarchia.

File di progetto (consigliato)

Altium: .PrjPcb, .PrjPcbStructure, .PrjPcbVariants. KiCad: .kicad_pro. Questi ci indicano la gerarchia e il foglio principale. Senza di essi, dovrai specificare il nome del foglio principale, oppure assumeremo un design piatto.

File *.bsdl (opzionale)

File Boundary Scan Description Language. Questi file utilizzano IEEE 1149.1-2013 per descrivere la capacità di test dei circuiti integrati digitali. Se forniti, Tomachie analizzerà la correttezza, la conformità e il Design-for-Test del tuo design.

Suggerimento: Quando richiedi gli schematici a un progettista o a un fornitore, chiedi i file di progetto (.PrjPcb o .kicad_pro) insieme ai file schematici. Molti progettisti dimenticano di includerli.