Przykładowe dokumenty przeglądu projektu

Standard ERC looks at nets. Tomachie looks at paths — verifying differential pair integrity and impedance continuity across the entire signal chain, even through passive components and connectors. It finds what's hidden: mischaracterized pins, broken impedance paths, and invisible property errors that break your layout wizards. These pre-generated reports show the full analysis output, each containing 10,000+ words of DFT analysis, EMC checks, PCOLA-SOQ scoring, connector pinouts, and testpoint coverage documentation:

- Przegląd projektu FPGA1394V3 — Interfejs IEEE 1394 FireWire z Xilinx XC7Z020 FPGA, analiza boundary scan BSDL, walidacja łańcucha JTAG

- Przegląd projektu MB1191 — Płytka rozwojowa STM32 Nucleo-144 z procesorem ARM Cortex-M

- Przegląd projektu TIDA-050036 — Projekt referencyjny płyty bazowej Texas Instruments dla przemysłu

Próbki do wypróbowania

- FPGA1394V3.zip — Interfejs IEEE 1394 FireWire z Xilinx FPGA, wieloarkuszowa hierarchia

- MB1191.zip — Płytka rozwojowa STM32 Nucleo-144 (ST Microelectronics)

- TIDA-050036.zip — Projekt referencyjny płyty bazowej Texas Instruments dla przemysłu

Pobierz dowolną próbkę, prześlij ją na stronie Prześlij i otrzymaj pełny raport analizy.

Przykładowe wyniki raportu

Tomachie generuje interaktywny raport HTML z sekcjami do nawigacji. Oto co otrzymasz:

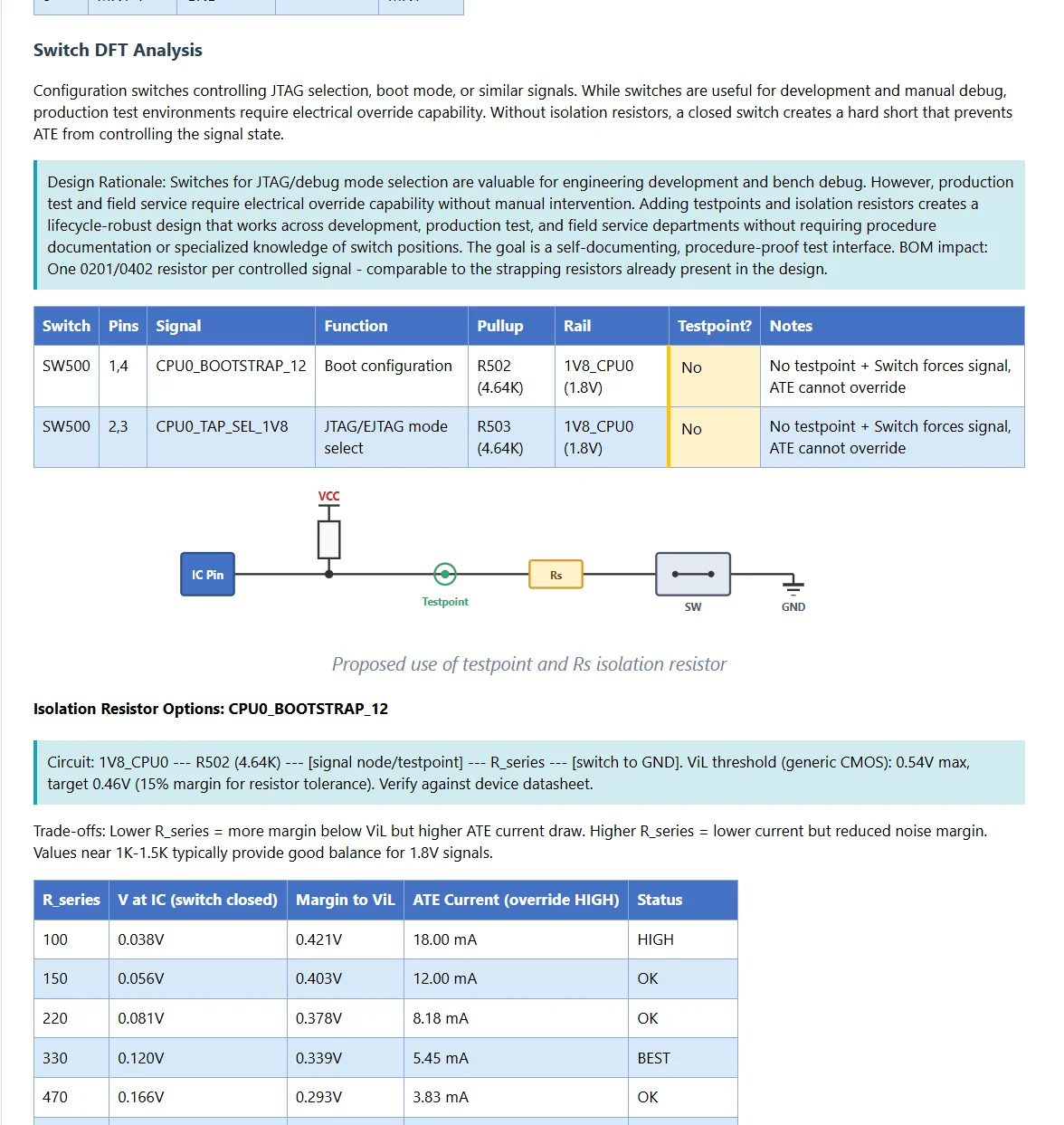

Analiza DFT przełączników — identyfikuje przełączniki konfiguracyjne bez możliwości nadpisania testowego, oblicza wartości rezystorów izolacyjnych dla kompatybilności z ATE.

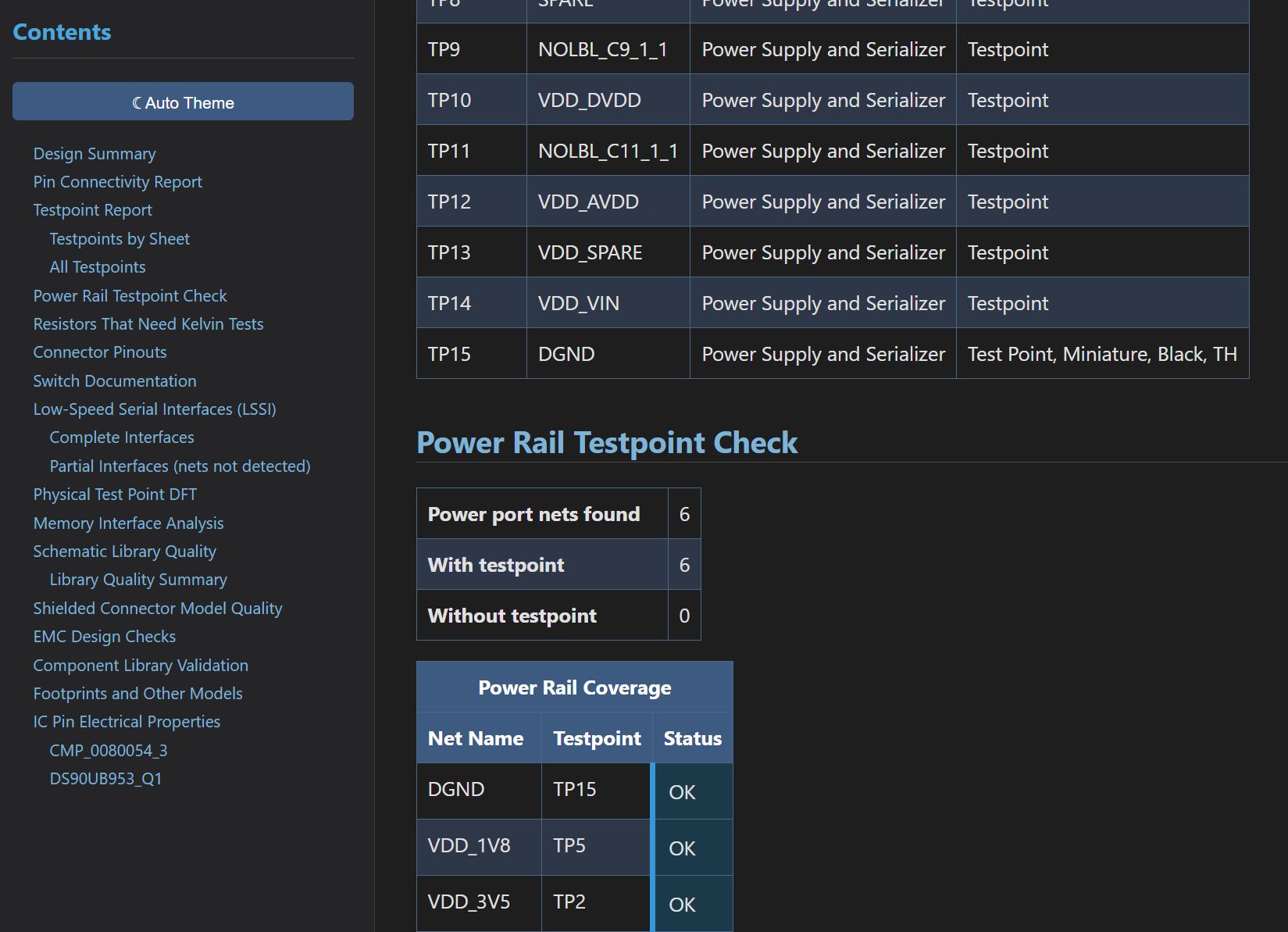

Inwentarz punktów testowych z analizą pokrycia szyn zasilania — każda sieć zasilania sprawdzona pod kątem dostępu testowego.

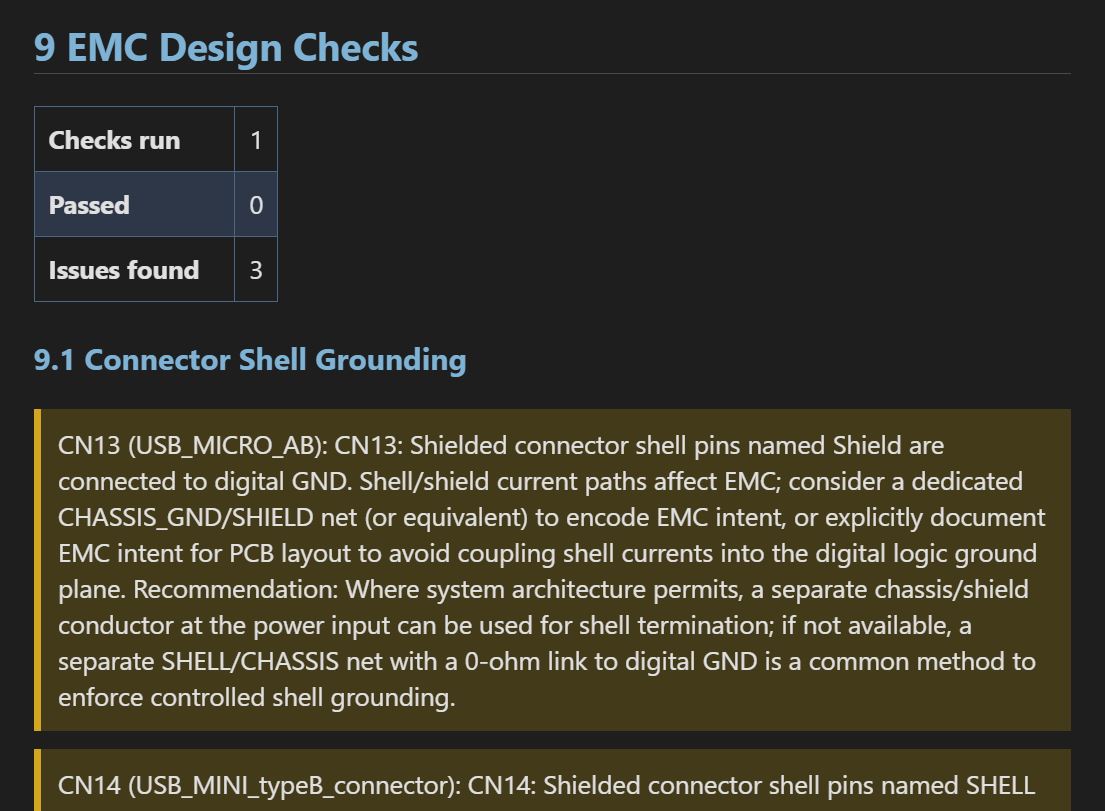

Sprawdzenia projektu EMC, walidacja bibliotek komponentów i audyt footprintów/modeli — wszystko w jednym raporcie.

Lewy panel nawigacyjny pozwala przejść bezpośrednio do dowolnej sekcji. Raporty zawierają Podsumowanie projektu, Łączność pinów, Interfejsy pamięci, Interfejsy szeregowe, Pinouty złączy, Analizę DFT, Oceny jakości bibliotek i więcej.

Obecny zakres: Projekty cyfrowe i mieszane — procesory, FPGA, interfejsy pamięci, magistrale szeregowe i analiza testowalności. Sprawdzenia specyficzne dla analogu (stabilność pętli zasilania, analiza filtrów) są w planie rozwoju.

Co przesłać

Spakuj pliki schematów do ZIP i prześlij. Oto co potrzebujemy:

Pliki schematów (wymagane)

Pliki Altium .SchDoc lub KiCad .kicad_sch — dołącz wszystkie arkusze, do których odwołuje się hierarchia.

Pliki projektu (zalecane)

Altium: .PrjPcb, .PrjPcbStructure, .PrjPcbVariants. KiCad: .kicad_pro. Określają one hierarchię i arkusz najwyższego poziomu. Bez nich musisz podać nazwę arkusza najwyższego poziomu, w przeciwnym razie założymy płaską strukturę projektu.

Pliki *.bsdl (opcjonalne)

Pliki Boundary Scan Description Language. Te pliki używają IEEE 1149.1-2013 do opisu możliwości testowania cyfrowych układów scalonych. Jeśli zostaną dostarczone, Tomachie przeanalizuje poprawność, zgodność i Design-for-Test Twojego projektu.

Wskazówka: Gdy prosisz projektanta lub wykonawcę o schematy, poproś o pliki projektu (.PrjPcb lub .kicad_pro) wraz z plikami schematów. Wielu projektantów zapomina je dołączyć.