ตัวอย่างเอกสารรีวิวการออกแบบ

Standard ERC looks at nets. Tomachie looks at paths — verifying differential pair integrity and impedance continuity across the entire signal chain, even through passive components and connectors. It finds what's hidden: mischaracterized pins, broken impedance paths, and invisible property errors that break your layout wizards. These pre-generated reports show the full analysis output, each containing 10,000+ words of DFT analysis, EMC checks, PCOLA-SOQ scoring, connector pinouts, and testpoint coverage documentation:

- รีวิวการออกแบบ FPGA1394V3 — อินเทอร์เฟซ IEEE 1394 FireWire พร้อม Xilinx XC7Z020 FPGA, การวิเคราะห์ BSDL Boundary Scan, การตรวจสอบ JTAG chain

- รีวิวการออกแบบ MB1191 — บอร์ดพัฒนา STM32 Nucleo-144 พร้อมโปรเซสเซอร์ ARM Cortex-M

- รีวิวการออกแบบ TIDA-050036 — การออกแบบอ้างอิงบอร์ดฐานอุตสาหกรรม Texas Instruments

ตัวอย่างที่คุณสามารถลองได้

- FPGA1394V3.zip — อินเทอร์เฟซ IEEE 1394 FireWire พร้อม Xilinx FPGA ลำดับชั้นหลายแผ่น

- MB1191.zip — บอร์ดพัฒนา STM32 Nucleo-144 (ST Microelectronics)

- TIDA-050036.zip — การออกแบบอ้างอิงบอร์ดฐานอุตสาหกรรม Texas Instruments

ดาวน์โหลดตัวอย่างใดก็ได้ อัปโหลดในหน้าส่งงาน และรับรายงานการวิเคราะห์ฉบับเต็ม

ตัวอย่างผลรายงาน

Tomachie สร้างรายงาน HTML เชิงโต้ตอบพร้อมส่วนที่สามารถนำทางได้ นี่คือสิ่งที่คุณจะได้รับ:

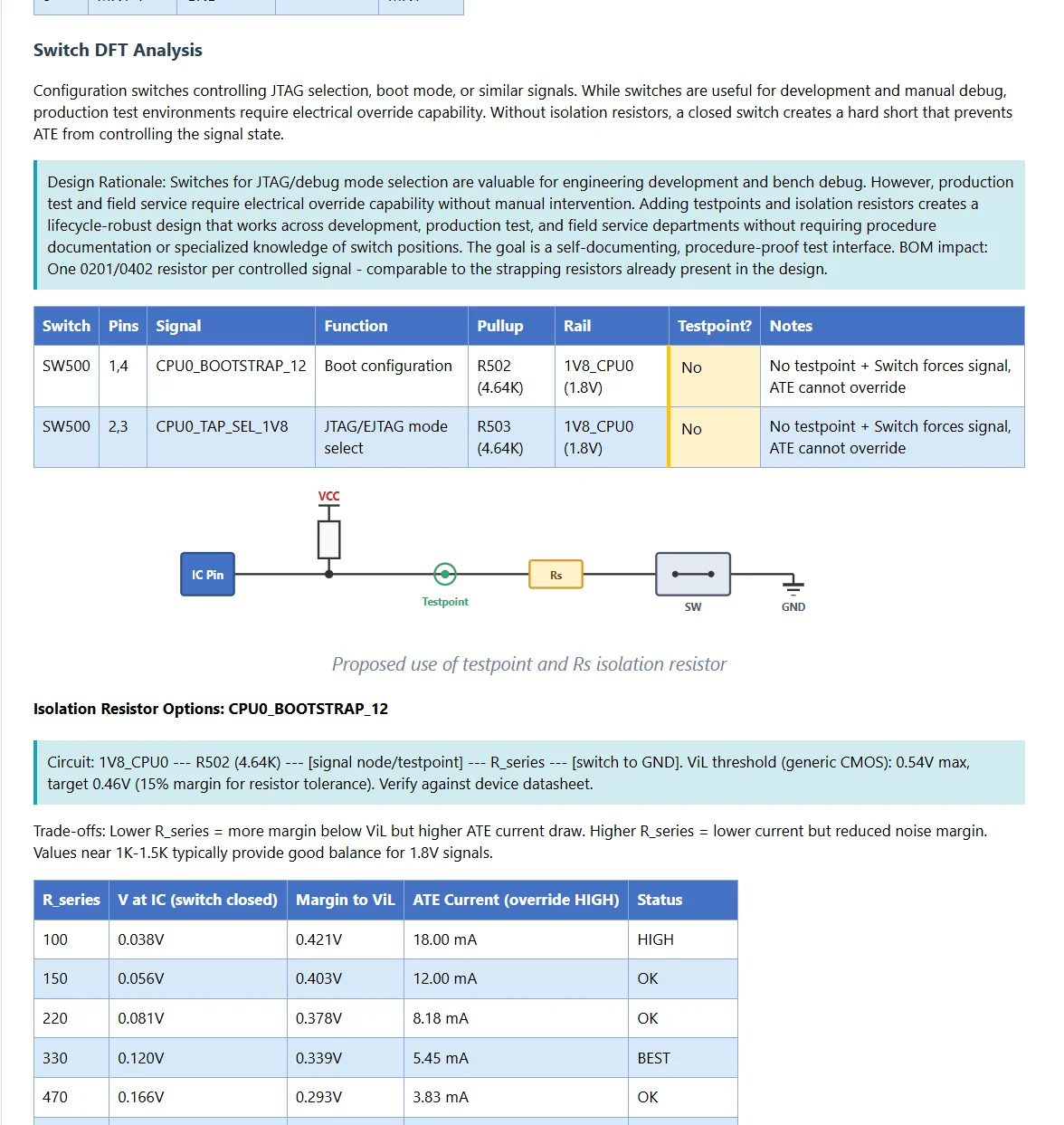

การวิเคราะห์ DFT สวิตช์ — ระบุสวิตช์กำหนดค่าที่ขาดความสามารถในการแทนที่การทดสอบ คำนวณค่าตัวต้านทานแยกสำหรับความเข้ากันได้กับ ATE

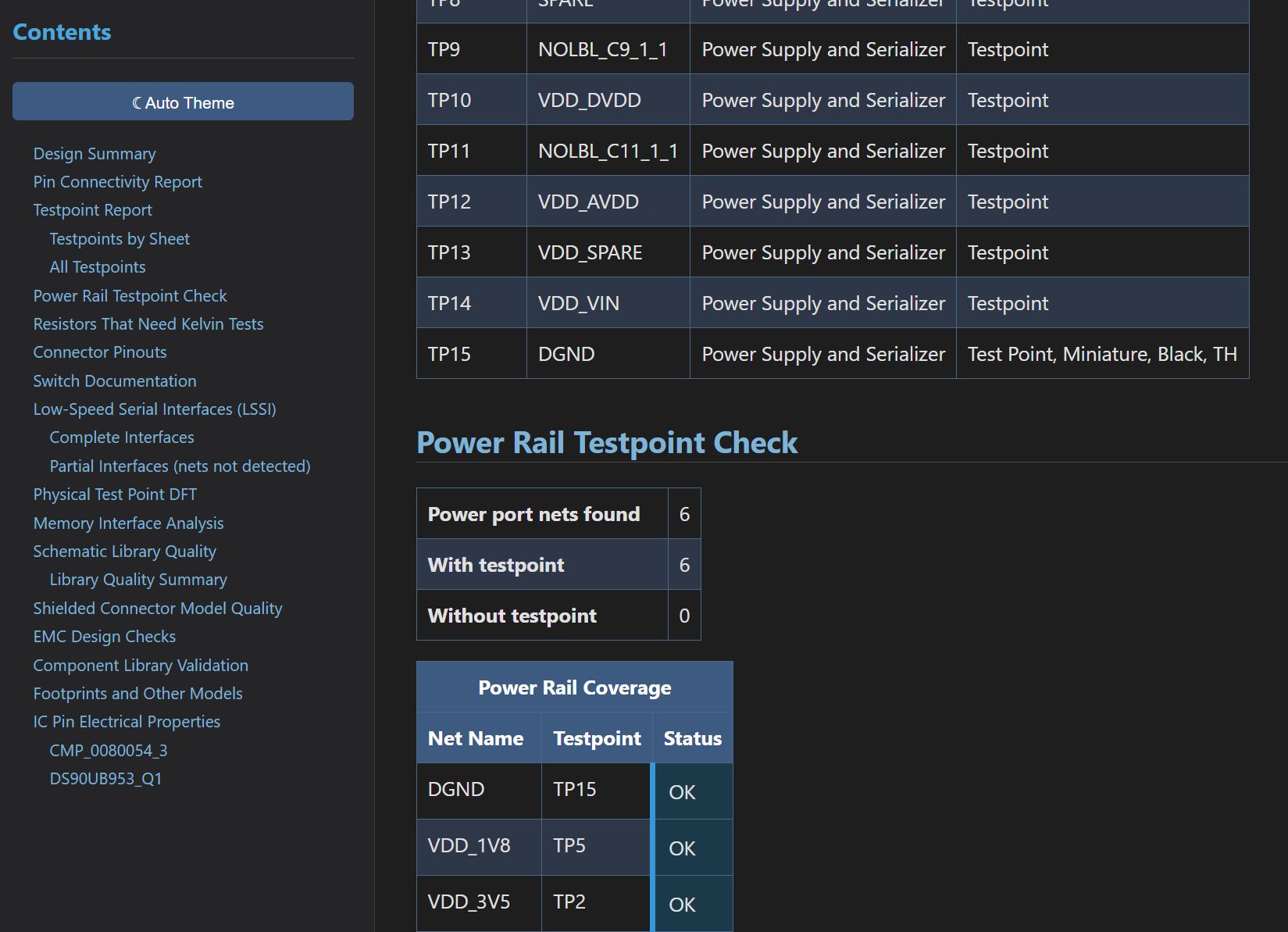

สินค้าคงคลังจุดทดสอบพร้อมการวิเคราะห์ครอบคลุมสายจ่ายไฟ — ตรวจสอบทุกเน็ตไฟสำหรับการเข้าถึงการทดสอบ

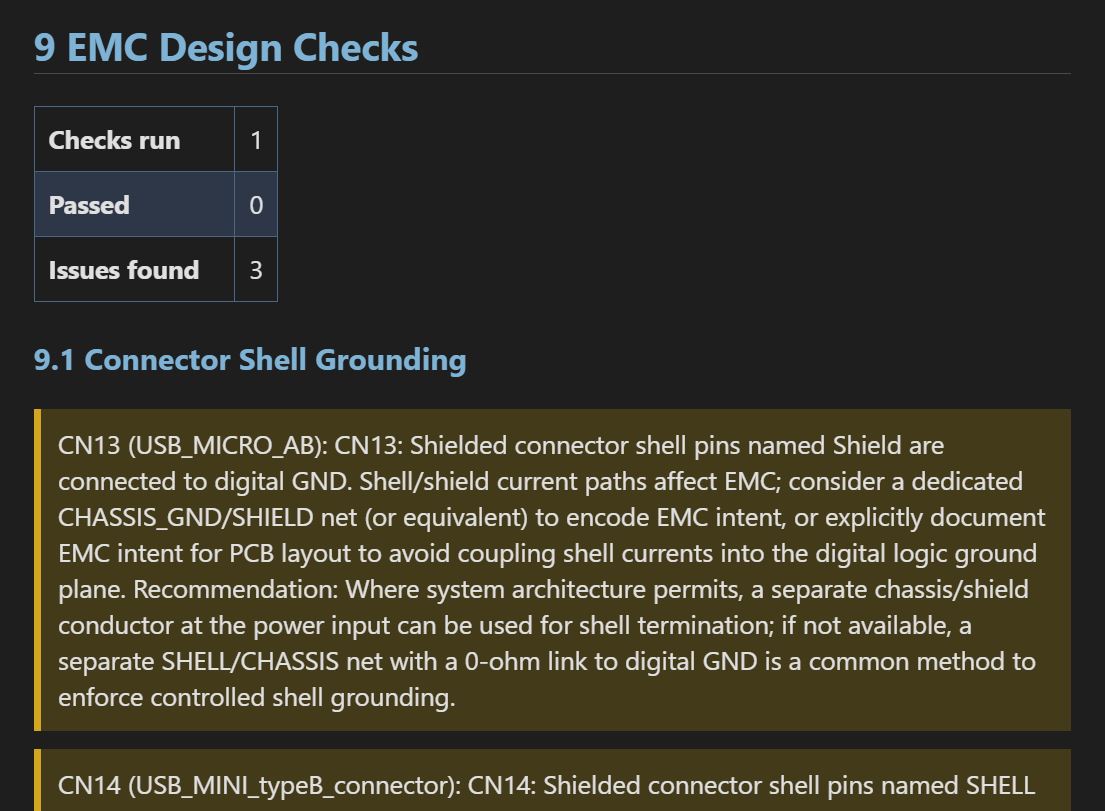

การตรวจสอบการออกแบบ EMC การตรวจสอบไลบรารีชิ้นส่วน และการตรวจสอบฟุตพริ้นท์/โมเดล — ทั้งหมดในรายงานเดียว

แผงนำทางด้านซ้ายช่วยให้คุณข้ามไปยังส่วนใดก็ได้โดยตรง รายงานประกอบด้วยสรุปการออกแบบ การเชื่อมต่อพิน อินเทอร์เฟซหน่วยความจำ อินเทอร์เฟซซีเรียล พินเอาต์คอนเนกเตอร์ การวิเคราะห์ DFT เกรดคุณภาพไลบรารี และอื่น ๆ

จุดเน้นปัจจุบัน: การออกแบบดิจิทัลและสัญญาณผสม — โปรเซสเซอร์, FPGA, อินเทอร์เฟซหน่วยความจำ, บัสซีเรียล และการวิเคราะห์ความสามารถในการทดสอบ การตรวจสอบเฉพาะอนาล็อก (ความเสถียรลูปแหล่งจ่ายไฟ การวิเคราะห์ฟิลเตอร์) อยู่ในแผนงาน

สิ่งที่ต้องอัปโหลด

บีบอัดไฟล์วงจรของคุณเป็น ZIP แล้วอัปโหลด นี่คือสิ่งที่เราต้องการ:

ไฟล์วงจร (จำเป็น)

ไฟล์ Altium .SchDoc หรือ KiCad .kicad_sch — รวมทุกแผ่นที่อ้างอิงโดยลำดับชั้น

ไฟล์โครงการ (แนะนำ)

Altium: .PrjPcb, .PrjPcbStructure, .PrjPcbVariants KiCad: .kicad_pro ไฟล์เหล่านี้บอกลำดับชั้นและแผ่นระดับบนสุดให้เรา หากไม่มี คุณจะต้องระบุชื่อแผ่นบนสุด หรือเราจะถือว่าเป็นการออกแบบแบบแบน

ไฟล์ *.bsdl (ไม่บังคับ)

ไฟล์ Boundary Scan Description Language ไฟล์เหล่านี้ใช้ IEEE 1149.1-2013 เพื่ออธิบายความสามารถในการทดสอบของ IC ดิจิทัล หากมี Tomachie จะวิเคราะห์ความถูกต้อง ความสอดคล้อง และ Design-for-Test ของการออกแบบของคุณ

เคล็ดลับ: เมื่อขอวงจรจากนักออกแบบหรือผู้รับเหมา ขอไฟล์โครงการ (.PrjPcb หรือ .kicad_pro) พร้อมกับไฟล์วงจรด้วย นักออกแบบหลายคนลืมรวมไว้